## conference

proceedings

# **18th USENIX Symposium on Operating Systems Design and** Implementation (OSDI '24)

Santa Clara, CA, USA July 10-12, 2024

# **OSDI '24 Sponsors**

**Platinum Sponsor**

**Diamond Sponsor**

**RBLOX**

**Gold Sponsors**

## **Silver Sponsors**

Bloomberg

## **Bronze Sponsors**

## **Open Access Sponsor**

# **USENIX Supporters**

**USENIX Patrons**

Futurewei • Google • Meta

**USENIX Benefactor**

Bloomberg

**USENIX Partner**

Thinkst Canary

**Open Access Supporter**

Google

**Open Access Publishing Partner**

PeerJ

## **USENIX** Association

# 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI '24)

July 10–12, 2024 Santa Clara, CA, USA

## © 2024 by The USENIX Association

## All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

ISBN 978-1-939133-40-3

## **Symposium Organizers**

**Program Co-Chairs**

Ada Gavrilovska, Georgia Institute of Technology

Douglas B. Terry, Amazon Web Services

**Program Committee**

Atul Adya, *Databricks* Nitin Agrawal, *Google*

Marcos K. Aguilera, VMware Research

Peter Alvaro, University of California, Santa Cruz Nadav Amit, Technion—Israel Institute of Technology

George Amvrosiadis, Carnegie Mellon University

Mahesh Balakrishnan, Confluent

Adam Belay, MIT CSAIL

Daniel S. Berger, *Microsoft Research* Abhishek Bhattacharjee, *Yale University*

Laurent Bindschaedler, Max Planck Institute for Software Systems

(MPI-SWS)

Ken Birman, Cornell University

Haibo Chen, Shanghai Jiao Tong University

Kang Chen, Tsinghua University

Vijay Chidambaram, The University of Texas at Austin

Byung-Gon Chun, Seoul National University and FriendliAI

Tyson Condie, *Databricks* Landon Cox, *Microsoft*

Natacha Crooks, University of California, Berkeley

Heming Cui, *University of Hong Kong* Angela Demke Brown, *University of Toronto*

Prabal Dutta, University of California, Berkeley

Jason Flinn, Meta

Pedro Fonseca, Purdue University

$Aishwarya\ Ganesan,\ University\ of\ Illinois\ at\ Urbana-Champaign$

and VMware Research

Roxana Geambasu, Columbia University

Jana Giceva, Technische Universität Munich

Moises Goldszmidt, Apple

Alexey Gotsman, *IMDEA Software Institute* Haryadi Gunawi, *University of Chicago*

Andreas Haeberlen, University of Pennsylvania and Roblox

Dongsu Han, Korea Advanced Institute of Science and

Technology (KAIST) Steven Hand, Google

Henry Hoffmann, University of Chicago

Jon Howell, VMware Research Ryan Huang, University of Michigan Rebecca Isaacs, Amazon Web Services Junchen Jiang, University of Chicago Sudarsun Kannan, Rutgers University Manos Kapritsos, University of Michigan

Sanidhya Kashyap, EPFL

Baris Kasikci, University of Washington

Anne-Marie Kermarrec, EPFL

Samira Khan, University of Virginia and Google

Ana Klimovic, ETH Zurich

Marios Kogias, *Imperial College London* Eddie Kohler, *Harvard University*

Dejan Kostic, KTH Royal Institute of Technology Arvind Krishnamurthy, University of Washington

Youngjin Kwon, Korea Advanced Institute of Science and

Technology (KAIST)

Baptiste Lepers, Université de Neuchâtel

Philip Levis, Stanford University

Jialin Li, National University of Singapore

Ming Liu, University of Wisconsin-Madison

Wyatt Lloyd, Princeton University

Jay Lorch, Microsoft Research

Shan Lu, Microsoft Research

Jonathan Mace, Microsoft Research Petros Maniatis, Google DeepMind

Z. Morley Mao, University of Michigan and Google

Changwoo Min, Igalia

Dushyanth Narayanan, Microsoft Research

Ravi Netravali, Princeton University

Jason Nieh, Columbia University

Shadi Noghabi, Microsoft Research

Amy Ousterhout, University of California, San Diego

Anand Padmanabha Iyer, Georgia Institute of Technology

Aurojit Panda, New York University

Amar Phanishayee, Microsoft Research

Peter Pietzuch, Imperial College London Costin Raiciu, University Politehnica of Bucharest

Luis Rodrigues, INESC-ID and Instituto Superior Técnico,

University of Lisbon

Timothy Roscoe, ETH Zurich

Malte Schwarzkopf, Brown University

Marc Shapiro, Sorbonne Université, LIP6, and Inria

Liuba Shrira, Brandeis University

Patrick Stuedi, Meta

Michael Stumm, University of Toronto

Adriana Szekeres, VMware Research

Amy Tai, Google

Alexey Tumanov, Georgia Institute of Technology

Dmitrii Ustiugov, Nanyang Technological University

Geoffrey M. Voelker, University of California, San Diego

Andy Warfield, Amazon

Hakim Weatherspoon, Cornell University and Exosteller, Inc.

Yubin Xia, Shanghai Jiao Tong University

Gala Yadgar, Technion—Israel Institute of Technology

Neeraja Yadwadkar, The University of Texas at Austin

Junfeng Yang, Columbia University

Ding Yuan, University of Toronto and YScope

Nickolai Zeldovich, Massachusetts Institute of Technology

Zheng Zhang, Amazon Web Services

Yuanyuan Zhou, University of California, San Diego

## **Poster Session Co-Chairs**

Aishwarya Ganesan, University of Illinois at Urbana-Champaign and VMware Research

Amy Ousterhout, University of California, San Diego

**Steering Committee**

Marcos K. Aguilera, VMware Research

Angela Demke Brown, University of Toronto

Casey Henderson-Ross, USENIX Association

Jon Howell, VMware Research

Kimberly Keeton, Google

${\it Jay Lorch}, {\it Microsoft Research}$

Shan Lu, University of Chicago

Timothy Roscoe, ETH Zurich

Geoff Voelker, University of California, San Diego

Hakim Weatherspoon, Cornell University and Exosteller, Inc.

## **External Reviewers**

# Message from the OSDI '24 Program Co-Chairs

Dear Colleagues,

Welcome to the 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI '24).

We are pleased that, once again, OSDI is co-located with the USENIX Annual Technical Conference (USENIX ATC '24). The two conferences combined are publishing a wide array of exciting papers representing some of the most innovative work in the systems research community. We hope you come away from OSDI and USENIX ATC with new colleagues, new friends, and new ideas.

This year, OSDI received 272 submissions. We accepted 49 submissions, which is an 18% acceptance rate. In addition to the papers accepted this year, 4 additional papers were accepted from the OSDI '23 Revise and Resubmit process. This brings the total program to 53 papers being published in the OSDI proceedings. We continue to be committed to a single-track conference at OSDI, and we have put together a 3-day program in which all papers are being presented in the same room so attendees can watch every single talk if they so desire.

To deal with the number and technical breadth of the OSDI submissions, we assembled a program committee of 95 members not counting us, the Program Co-Chairs. Reviewing papers is a time-consuming task that requires high judgment, and we are grateful to the program committee for their diligence, professionalism, and cooperation during the review process. We are proud that OSDI is known for high quality reviews that help authors to produce their very best work and present it clearly to our community.

The program committee reviewed submissions in two rounds. Every paper received at least three reviews in the first round. Select papers then received 2 or 3 additional reviews in the second round. The accepted papers were chosen based on an online discussion phase and a two-day PC meeting. The committee completed more than 1,000 reviews and posted hundreds of comments as part of the online discussion process. Each accepted paper was assigned a shepherd to work with the authors to revise the paper in response to reviewer feedback.

OSDI '24 had an artifact-evaluation committee, shared with USENIX ATC '24, that organized and evaluated the artifacts submitted by authors. The committee co-chairs this year were Jianyu Jiang, Ji Qi, and Cesar A. Stuardo. The committee made one recommendation for a Distinguished Artifact Award.

OSDI '24 had a poster submission process that was run by Aishwarya Ganesan and Amy Ousterhout, who graciously took on this task in addition to serving on the PC. They accepted 52 posters for display at the OSDI poster session, representing a mix of posters from papers presented at the conference as well as other work.

Once the accepted papers were decided, we began the process of deciding on the Jay Lepreau Best Paper Awards. A small committee of non-conflicted PC members read all of the top-ranked papers and agreed on the award recommendation.

As PC chairs, we are grateful to so many dedicated volunteers and professional staff whose efforts have made this conference a reality. We thank the authors who submitted such high-quality work. This conference is first and foremost a forum for disseminating, sharing, discussing, and debating world-class systems research. Thank you for your hard work and innovation! We thank the PC members and external reviewers for their significant investment of time, energy, and insight into shaping the program. We thank Vaibhav Bhosale and Vishal Suresh Rao, who helped us during the PC meeting and made sure we ran the technology and not the other way around. We especially thank the USENIX staff who have made chairing a conference like this one a well-oiled machine! Finally, we thank you for coming to this conference to engage with each other and with the authors of the accepted papers.

We are honored to have served as the OSDI '24 Program Co-Chairs. Thank you for entrusting us with this important role. We hope that you enjoy the conference!

Ada Gavrilovska, *Georgia Institute of Technology* Doug Terry, *Amazon Web Services* OSDI '24 Program Co-Chairs

# 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI '24)

## July 10–12, 2024 Santa Clara, CA, USA

## Wednesday, July 10

| Memory Management                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Sabre: Hardware-Accelerated Snapshot Compression for Serverless MicroVMs</b>                                                                                                           |

| Nomad: Non-Exclusive Memory Tiering via Transactional Page Migration                                                                                                                      |

| Managing Memory Tiers with CXL in Virtualized Environments                                                                                                                                |

| Harvesting Memory-bound CPU Stall Cycles in Software with MSH                                                                                                                             |

| A Tale of Two Paths: Toward a Hybrid Data Plane for Efficient Far-Memory Applications                                                                                                     |

| DRust: Language-Guided Distributed Shared Memory with Fine Granularity, Full Transparency, and                                                                                            |

| Ultra Efficiency                                                                                                                                                                          |

| Low-Latency LLM Serving                                                                                                                                                                   |

| Taming Throughput-Latency Tradeoff in LLM Inference with Sarathi-Serve                                                                                                                    |

| ServerlessLLM: Low-Latency Serverless Inference for Large Language Models                                                                                                                 |

| InfiniGen: Efficient Generative Inference of Large Language Models with Dynamic KV Cache Management 155 Wonbeom Lee, Jungi Lee, Junghwan Seo, and Jaewoong Sim, Seoul National University |

| Llumnix: Dynamic Scheduling for Large Language Model Serving                                                                                                                              |

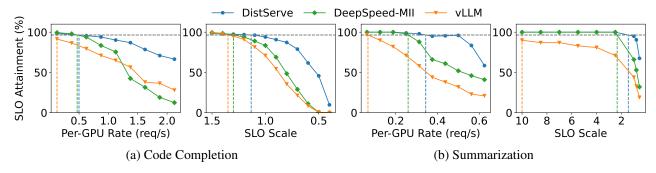

| DistServe: Disaggregating Prefill and Decoding for Goodput-optimized Large Language Model Serving                                                                                         |

| Distributed Systems                                                                         |

|---------------------------------------------------------------------------------------------|

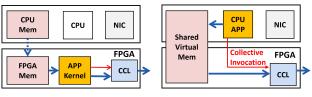

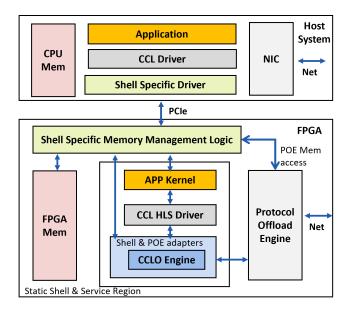

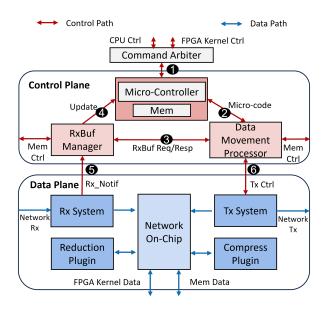

| ACCL+: an FPGA-Based Collective Engine for Distributed Applications                         |

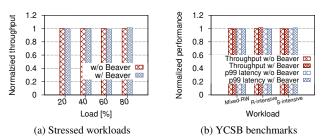

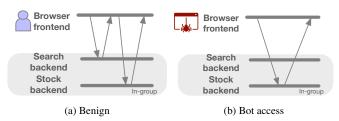

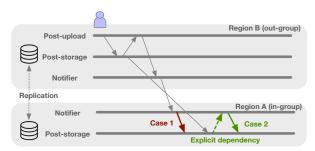

| Beaver: Practical Partial Snapshots for Distributed Cloud Services                          |

| Fast and Scalable In-network Lock Management Using Lock Fission                             |

| Chop Chop: Byzantine Atomic Broadcast to the Network Limit                                  |

| Thursday, July 11                                                                           |

| Deep Learning                                                                               |

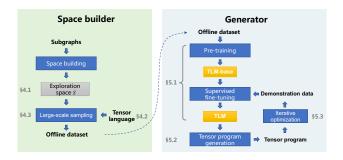

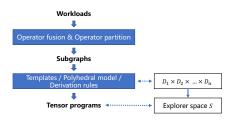

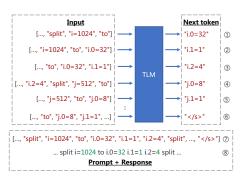

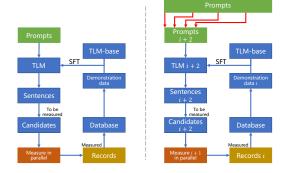

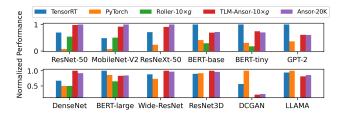

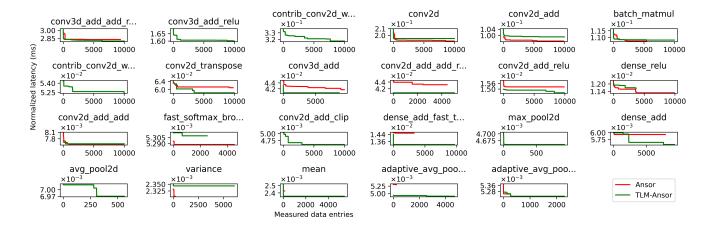

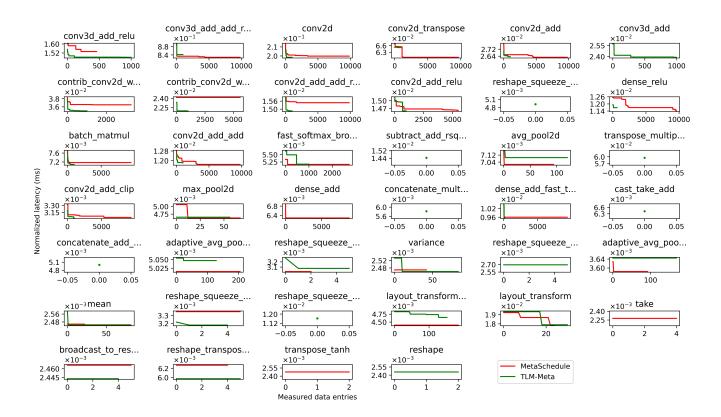

| Enabling Tensor Language Model to Assist in Generating High-Performance Tensor Programs for |

| Deep Learning                                                                               |

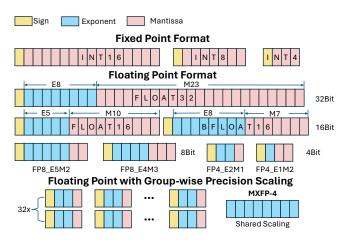

| LADDER: Enabling Efficient Low-Precision Deep Learning Computing through Hardware-aware     |

| Tensor Transformation                                                                       |

| CARAVAN: Practical Online Learning of In-Network ML Models with Labeling Agents             |

| nnScaler: Constraint-Guided Parallelization Plan Generation for Deep Learning Training      |

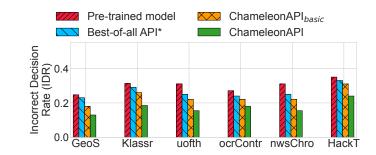

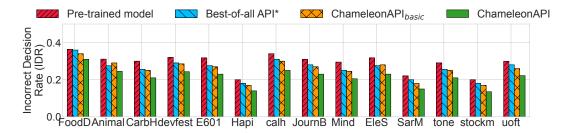

| ChameleonAPI: Automatic and Efficient Customization of Neural Networks for ML Applications  |

| Operating Systems                                                                           |

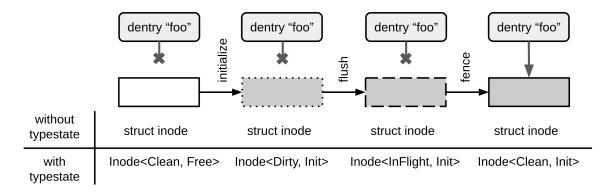

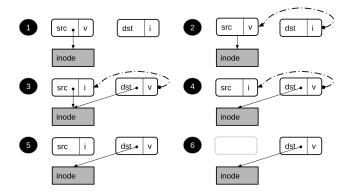

| SquirrelFS: using the Rust compiler to check file-system crash consistency                  |

| High-throughput and Flexible Host Networking for Accelerated Computing                                                                                                                                                                                                                                                                                                                                           |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

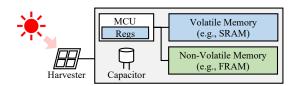

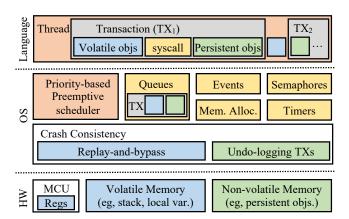

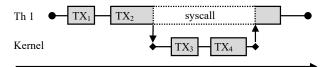

| IntOS: Persistent Embedded Operating System and Language Support for Multi-threaded Intermittent Computing.  Yilun Wu, Stony Brook University; Byounguk Min, Purdue University; Mohannad Ismail and Wenjie Xiong, Virginia Tech; Changhee Jung, Purdue University; Dongyoon Lee, Stony Brook University                                                                                                          | 425 |

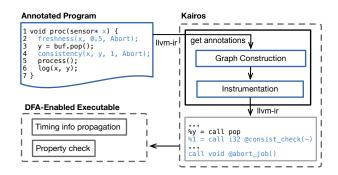

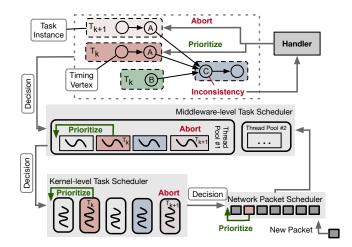

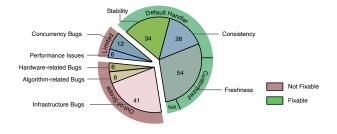

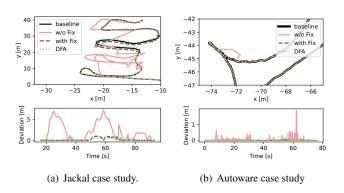

| Data-flow Availability: Achieving Timing Assurance in Autonomous Systems                                                                                                                                                                                                                                                                                                                                         | 445 |

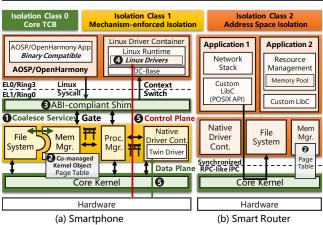

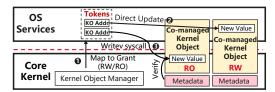

| Microkernel Goes General: Performance and Compatibility in the HongMeng Production Microkernel                                                                                                                                                                                                                                                                                                                   | 465 |

| Cloud Computing                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| When will my ML Job finish? Toward providing Completion Time Estimates through Predictability-Centric Scheduling                                                                                                                                                                                                                                                                                                 | 197 |

| Abdullah Bin Faisal, Noah Martin, Hafiz Mohsin Bashir, Swaminathan Lamelas, and Fahad R. Dogar, <i>Tufts University</i>                                                                                                                                                                                                                                                                                          | 40/ |

| Optimizing Resource Allocation in Hyperscale Datacenters: Scalability, Usability, and Experiences                                                                                                                                                                                                                                                                                                                | 507 |

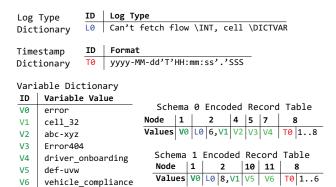

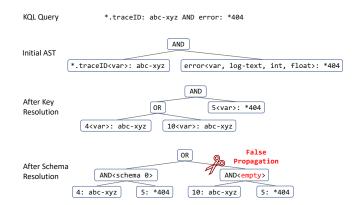

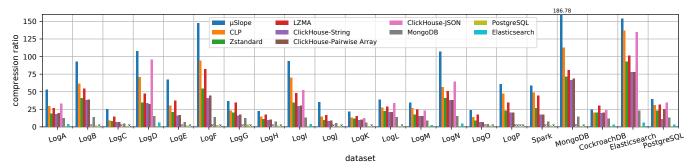

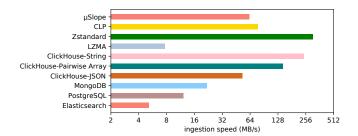

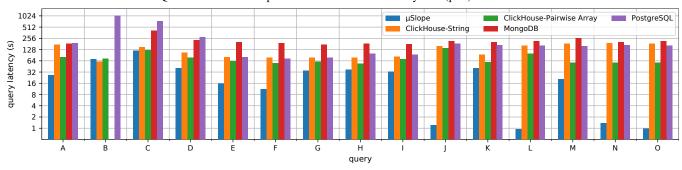

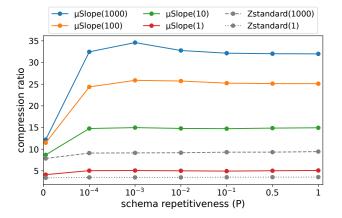

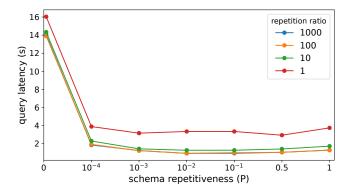

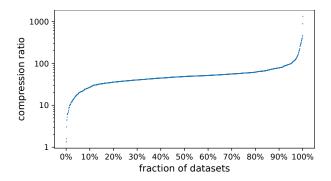

| μSlope: High Compression and Fast Search on Semi-Structured Logs                                                                                                                                                                                                                                                                                                                                                 | 529 |

| ServiceLab: Preventing Tiny Performance Regressions at Hyperscale through Pre-Production Testing                                                                                                                                                                                                                                                                                                                 | 1,  |

| MAST: Global Scheduling of ML Training across Geo-Distributed Datacenters at Hyperscale  Arnab Choudhury, Meta Platforms; Yang Wang, Meta Platforms and The Ohio State University; Tuomas Pelkonen, Meta Platforms; Kutta Srinivasan, LinkedIn; Abha Jain, Shenghao Lin, Delia David, Siavash Soleimanifard, Michael Chen, Abhishek Yadav, Ritesh Tijoriwala, Denis Samoylov, and Chunqiang Tang, Meta Platforms |     |

| Formal Verification                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Automatically Reasoning About How Systems Code Uses the CPU Cache                                                                                                                                                                                                                                                                                                                                                | 581 |

| VERISMO: A Verified Security Module for Confidential VMs                                                                                                                                                                                                                                                                                                                                                         | 599 |

| Validating the eBPF Verifier via State Embedding                                                                                                                                                                                                                                                                                                                                                                 | 615 |

| Using Dynamically Layered Definite Releases for Verifying the RefFS File System                                                                                                                                                                                                                                                                                                                                  |     |

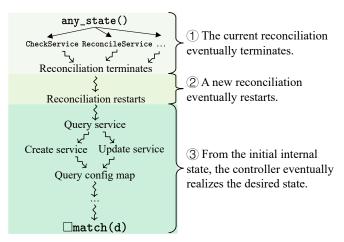

| Anvil: Verifying Liveness of Cluster Management Controllers                                                                                                                                                                                                                                                                                                       | 649 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Friday, July 12                                                                                                                                                                                                                                                                                                                                                   |     |

| Cloud Security                                                                                                                                                                                                                                                                                                                                                    |     |

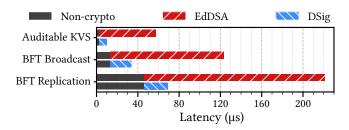

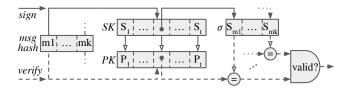

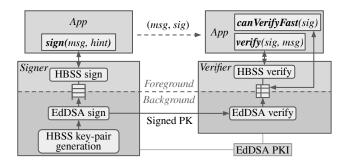

| <b>DSig: Breaking the Barrier of Signatures in Data Centers</b>                                                                                                                                                                                                                                                                                                   | 667 |

| Ransom Access Memories: Achieving Practical Ransomware Protection in Cloud with DeftPunk Zhongyu Wang, Yaheng Song, Erci Xu, Haonan Wu, Guangxun Tong, Shizhuo Sun, Haoran Li, Jincheng Liu, Lijun Ding, Rong Liu, Jiaji Zhu, and Jiesheng Wu, <i>Alibaba Group</i>                                                                                               |     |

| Secret Key Recovery in a Global-Scale End-to-End Encryption System                                                                                                                                                                                                                                                                                                | 703 |

| Flock: A Framework for Deploying On-Demand Distributed Trust                                                                                                                                                                                                                                                                                                      | 721 |

| Data Management                                                                                                                                                                                                                                                                                                                                                   |     |

| FairyWren: A Sustainable Cache for Emerging Write-Read-Erase Flash Interfaces                                                                                                                                                                                                                                                                                     | 745 |

| Massively Parallel Multi-Versioned Transaction Processing                                                                                                                                                                                                                                                                                                         | 765 |

| Burstable Cloud Block Storage with Data Processing Units                                                                                                                                                                                                                                                                                                          | 783 |

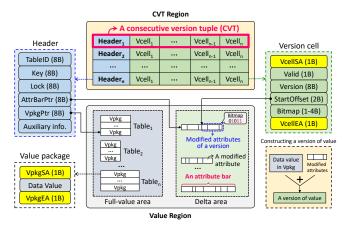

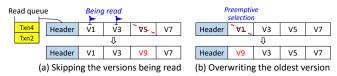

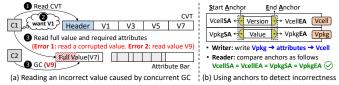

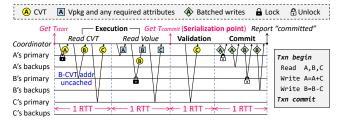

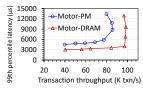

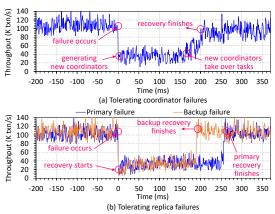

| Motor: Enabling Multi-Versioning for Distributed Transactions on Disaggregated Memory                                                                                                                                                                                                                                                                             | 801 |

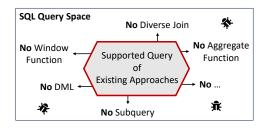

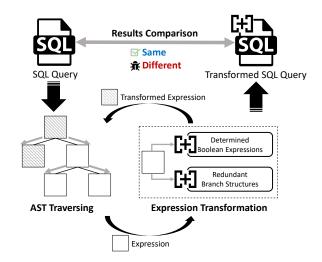

| Analysis of Correctness                                                                                                                                                                                                                                                                                                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                   | 821 |

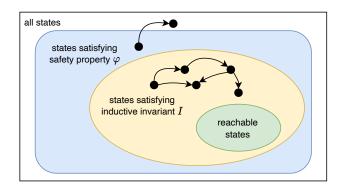

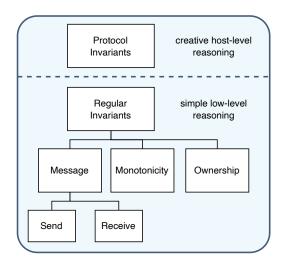

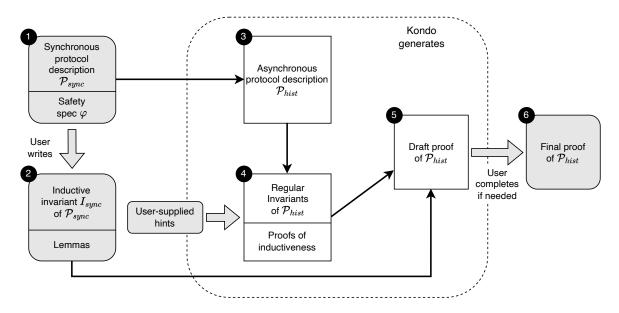

| Inductive Invariants That Spark Joy: Using Invariant Taxonomies to Streamline Distributed Protocol Proofs Tony Nuda Zhang, <i>University of Michigan</i> ; Travis Hance, <i>Carnegie Mellon University</i> ; Manos Kapritsos, <i>University of Michigan</i> ; Tej Chajed, <i>University of Wisconsin–Madison</i> ; Bryan Parno, <i>Carnegie Mellon University</i> | 837 |

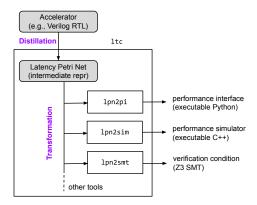

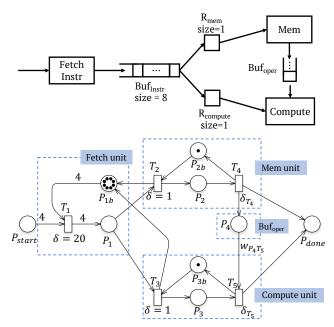

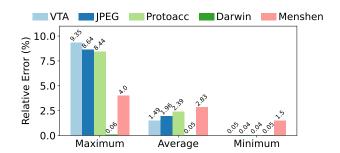

| Performance Interfaces for Hardware Accelerators                                                                                                                                                                                                                                                                                                                  | 855 |

| IronSpec: Increasing the Reliability of Formal Specifications                                                                                                                                                                                                                                                                                                     | 875 |

| Identifying On-/Off-CPU Bottlenecks Together with Blocked Samples                                                                                                                                                                                                                                                                                                 | 893 |

| ML Scheduling                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------|

| dLoRA: Dynamically Orchestrating Requests and Adapters for LoRA LLM Serving                                                  |

| Parrot: Efficient Serving of LLM-based Applications with Semantic Variable                                                   |

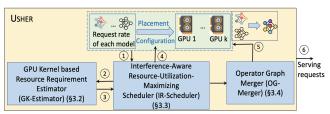

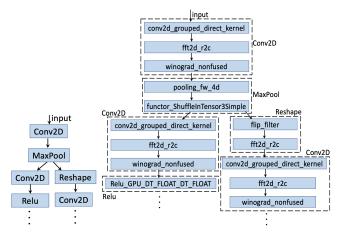

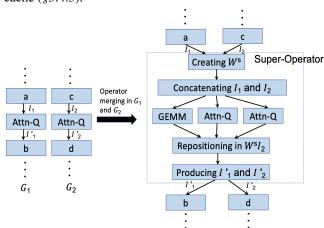

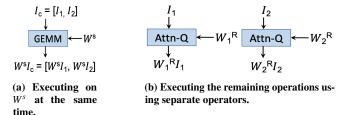

| USHER: Holistic Interference Avoidance for Resource Optimized ML Inference                                                   |

| Fairness in Serving Large Language Models                                                                                    |

| MonoNN: Enabling a New Monolithic Optimization Space for Neural Network Inference Tasks on Modern  GPU-Centric Architectures |

## Sabre: Hardware-Accelerated Snapshot Compression for Serverless MicroVMs

Nikita Lazarev Varun Gohil James Tsai<sup>†</sup> Andy Anderson<sup>†</sup> Bhushan Chitlur<sup>†</sup> Zhiru Zhang<sup>§</sup> Christina Delimitrou MIT, CSAIL †Intel Labs §Cornell University

## **Abstract**

MicroVM snapshotting significantly reduces the cold start overheads in serverless applications. Snapshotting enables storing part of the physical memory of a microVM guest into a file, and later restoring from it to avoid long cold start-up times. Prefetching memory pages from snapshots can further improve the effectiveness of snapshotting. However, the efficacy of prefetching depends on the size of the memory that needs to be restored. Lossless page compression is therefore a great way to improve the coverage of the memory footprint that snapshotting with prefetching achieves. Unfortunately, the high overhead and high CPU cost of software-based (de)compression make this impractical.

We introduce Sabre, a novel approach to snapshot page prefetching based on hardware-accelerated (de)compression. Sabre leverages an increasingly pervasive near-memory analytics accelerator available in modern datacenter processors. We show that by appropriately leveraging such accelerators, microVM snapshots of serverless applications can be compressed up to a factor of 4.5×, with nearly negligible decompression costs. We use this insight to build an efficient page prefetching library capable of speeding up memory restoration from snapshots by up to 55%. We integrate the library with the production-grade Firecracker microVMs and evaluate its end-to-end performance on a wide set of serverless applications.

## Introduction

Serverless is an emerging cloud computing paradigm gaining widespread popularity across applications of different classes, from lightweight interactive services [73] to highly data-parallel applications, such as machine learning and video encoding [21,24,40,47,67]. Serverless offers a Function-as-a-Service (FaaS) execution model, where applications instantiate short-lived, fine-grained resources on-demand without the overhead of provisioning and deployment typical cloud environments incur. When requests are processed, the resources

are terminated, achieving a pay-as-you-go model. This both avoids resource overprovisioning, which has been a longstanding issue with cloud infrastructures [22, 28, 58] and reduces the end-to-end deployment cost [33, 46].

Serverless is based on lightweight virtualization/isolation technologies [19] such as Docker, Google gVisor [3], Kata containers [10], NEC's LightVMs [53], and AWS Firecracker microVMs [17]. These technologies implement sandboxes for executing containerized applications with different levels of isolation. For example, gVisor implements a lightweight user space kernel capable of executing most of the system calls within the sandbox. On the other hand, Firecracker is a full lightweight virtualization technology, based on KVM, which can boot standard Linux kernels in sub-second time [17]. Due to the high isolation guarantees of microVMs, security, and performance, Firecracker is widely used in serverless clouds.

Despite its advantages, serverless and microVMs introduce a few critical overheads to performance. A major overhead is cold starts (or cold boots) – the overhead of the initial boot of container sandboxes upon a function invocation. Both industry and academia have proposed numerous techniques to mitigate cold start overheads [31,35,64,73], with one of the most promising being VM snapshotting [31]. VM snapshots capture the current state of the VM and its physical memory and save them in a file. During the next boot, the guest system is restored from the file instead of booting from scratch. Several different techniques can be used to make snapshots, depending on which parts of the guest's physical memory should be saved. For instance, Firecracker can snapshot the full guest memory or only the dirty pages. Additionally, recent studies have proposed using working sets of pages [71] to make serverless VM snapshots smaller, faster to fetch, and overall more efficient [20,64] in reducing cold starts. However, independent of the underlying techniques used to create snapshots, the overhead of storing and prefetching them is non-negligible. Unfortunately, the latter is on the critical path of VM restoration and therefore directly impacts cold starts.

Reducing the size of snapshots can make them significantly more efficient, for example through lossless memory compression. While memory compression has been used in domains where the application performance is not critical (e.g., *zswap* [39], *zram* [38] in Android OS for mobile devices), in serverless the restoration of a memory snapshot is on the critical path, precluding the use of existing software-based (de)compression algorithms. At the same time, there are numerous hardware implementations of (de)compression [23, 41, 51, 52, 56], however, they had not, until now, been implemented in mainstream datacenter processors [43]. In particular, Intel recently released the In-Memory Analytics Accelerator (IAA) [6] in their 4<sup>th</sup> Gen Xeon Scalable CPUs, which enables efficient compression for datacenter applications at scale.

We present Sabre, a hardware-accelerated *general-purpose* memory prefetching system, which uses lossless compression mechanisms, such as IAA, to compress and restore microVM snapshots. This paper makes two major contributions. First, we characterize, for the first time, the IAA accelerator on a set of diverse benchmarks, and show its potential for compressing memory pages. We show that IAA can compress pages by  $2-4.5\times$ , depending on the underlying page selection algorithm. Moreover, we show that decompression can be done up to  $10\times$  faster with hardware acceleration, and with careful design, this time can be entirely hidden behind the disk I/O and page fault handling. This results in near-free decompression in terms of the overall memory restoration latency, while reducing the size and the loading time of snapshot pages.

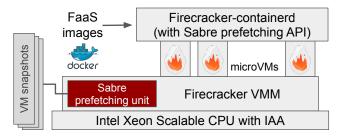

Second, based on this characterization, we build Sabre and integrate it with the Firecracker virtual machine monitor (VMM) in a serverless environment with snapshotting support. Sabre is agnostic to the underlying page snapshotting policy, it operates entirely in the host's user space, and interacts with the IAA accelerator via the Shared Virtual Memory (SVM) mechanism. The latter enables out-of-box and transparent integration of Sabre with existing VMMs at scale.

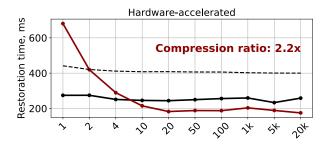

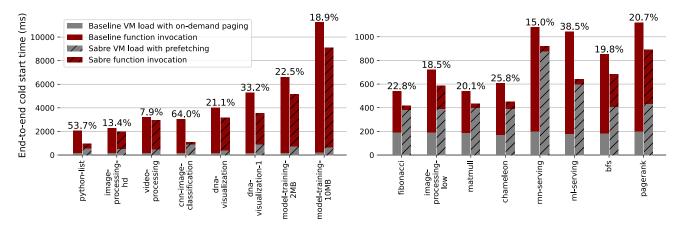

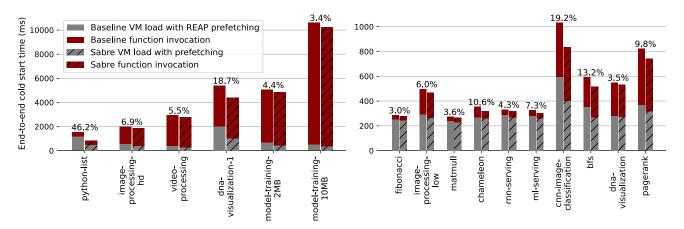

We evaluate Sabre on its efficiency in restoring microVMs from snapshots across a wide range of end-to-end serverless applications using two methods of creating snapshots: dirty page-based and working set-based. We show that Sabre compresses microVM snapshots up to  $4.5\times$  without introducing any decompression overheads. Moreover, we show that Sabre enables up to 55% faster memory restoration, which results in an additional reduction of the end-to-end cold start time by 20% with respect to already optimized state-of-the-art snapshotting baselines.

Sabre is open-source software and it is available at the following link [13].

## 2 Background

## 2.1 MicroVMs for Serverless

Serverless is gaining popularity across many application domains by reducing the cloud provisioning overhead and enabling higher elasticity for applications with high parallelism and intermittent activity. Lightweight virtualization technologies (or microVMs) became a popular choice for cloud providers due to the isolation and fast instantiation they provide [17,69]. Fully virtualized VMs running over Type-1 hypervisors, such as KVM [37] or Hyper-V [70], allow isolating tenants down to hardware and provide the highest security guarantees for applications running in the cloud. On the other hand, microVMs are much faster to boot and have a much smaller memory footprint than traditional Type-1 virtual machines. This means that microVMs achieve the best of both worlds between containers and Type-1 hypervisors. MicroVMs are widely used in serverless, where applications require both strong isolation guarantees and fast start-up.

Modern microVMs, such as AWS Firecracker [17], use several optimizations to boot up in sub-seconds. However, booting the VM itself is only part of the end-to-end application execution latency [31,64], with a significant component corresponding to the initialization of the software dependencies after the boot. For applications based on complex multilayer stacks, such as gRPC servers and JavaScript runtimes, bringing up the dependencies might be as high as several seconds [31]. Additionally, the applications themselves can contain long-running initialization routines, which also contribute to end-to-end latency. For example, machine learning (ML) services need to load the models before serving inference queries. Altogether, this makes the end-to-end execution of the first batch of requests running on freshly booted microVMs an order of magnitude slower than subsequent requests. This is known as cold start, and all microVMs are prone to it.

Mitigating cold starts is one of the most well-researched aspects of microVMs [65]. Existing solutions range from scheduling techniques optimized for specific applications to runtime and infrastructure optimizations [54, 73]. One solution that is generally agnostic to applications is VM snapshotting [31].

## 2.2 MicroVM Snapshotting and Prefetching

Snapshotting is a technology that allows storing the VM state and guest OS physical memory in a file in the local or remote filesystem. Snapshots are usually created after the VM and the application logic with all its dependencies are fully initialized and ready to serve requests. Upon the next invocation of the VM the hypervisor restores the VM state and guest memory from the snapshot, instead of booting the VM from scratch. This dramatically reduces cold start overheads.

In the most basic case, snapshots contain the entire guest physical memory. Some hypervisors, such as Firecracker, also allow dirty-memory tracking, which only stores the dirty guest pages as seen by the hypervisor. Snapshots can be organized hierarchically following the software dependencies of applications [31]. However, recovering from snapshots is far from

free. In some cases, the size of the snapshots can be as high as the whole guest memory, therefore precluding the possibility of loading pages from snapshots in advance. For this reason, existing commercial microVMs implement memory restoration via on-demand paging. Unfortunately, on-demand paging yields a lot of page faults on the critical path of the restoration from snapshots, which slows down request execution.

A way to reduce the overhead of page faults is to enable prefetching of pages from snapshots. This can be efficiently done through, for example, working set (WS) estimation. This approach has been used to create VM checkpoints [71], and recently – for serverless microVMs [64]. Here, each snapshot is accommodated in a WS file, storing pages that are likely to be accessed during subsequent invocations. There are different ways of constructing WS files [20, 64, 71] according to various working set estimation techniques. For example, in Record-and-Replay (REAP) [64], the authors propose to record all guest pages being accessed during the first invocation of serverless functions and put them into the WS file. Upon the next invocation, the WS file can be prefetched from the disk, and the WS pages can be installed in the guest's memory to speed up the next cold invocations. REAP works well for applications with a similar working set across different invocations of the same function. When this does not hold, REAP can fail to deliver good performance; in this case, prefetching some other subset of dirty pages (or even all dirty pages) can be more beneficial. Snapshots generally consume a lot of disk space and require cloud providers to carefully provision their storage resources [2]. Even workingset-based snapshots can sometimes be as large as a few hundred megabytes [20]. This is non-negligible given that a single server might host hundreds of microVMs.

Independently of the underlying technique to create microVM snapshots and/or WS files, the efficiency of prefetching depends on the memory size that needs to be restored from the disk into the guest memory. A general rule to make prefetching-based techniques more efficient is to reduce the size of the snapshots/WS files. This also reduces the disk space needed to store snapshots. This size reduction can be achieved through memory compression. However, memory restoration happens on the critical path of the VM boot-up, and for compression algorithms with high deflate ratios, the decompression might take a long time. Moreover, such algorithms usually consume a lot of CPU time for compression and therefore VM snapshotting. This makes the use of software memory compression for microVM snapshotting undesirable.

#### Hardware-Accelerated (De)Compression 2.3

Software-based memory compression has been extensively used in applications where performance is not critical. For example, zram [38] is used in Android OS on mobile devices, while zswap [39] can improve the efficiency of memory swapping for non-performance critical applications. Unfortunately, this does not apply to microVM memory restoration, where decompression directly impacts the cold start overhead.

There have been many proposals for accelerating memory compression in hardware. For example, Pekhimenko et. al. [56] propose base-delta compression for on-chip caches. Hoyong et. al. [41] derive a novel compression algorithm for GPU memory. Li et al. [52] introduced a hardware accelerator for the compression of genome sequences. All such proposals are based on application-specific, special-purpose compression accelerators and algorithms, and therefore have never been implemented on commodity datacenter processors. Many (de)compression accelerators are based on FPGA cards [25, 34, 50, 57] which are only available in a small set of public clouds. However, the demand for general-purpose (de)compression acceleration at scale is actively growing.

(De)Compression is known to be one of the major sources of datacenter tax [36,42,61]. A recent study from Google [36] showed that compression accounts for up to 30% of cycles for large-scale database applications, such as BigTable and Big-Query [32,62], and it is also extensively used in many other applications. This motivates cloud providers and chip vendors to build efficient hardware accelerators [43] for general-purpose lossless (de)compression. The primary use cases for such accelerators are databases and query-processing engines. In particular, Intel recently introduced the In-Memory Analytic Accelerator (IAA), which is now part of commodity datacenter processors, such as the Xeon 4<sup>th</sup> Generation CPUs, which are already widely available. This accelerator can perform DEFLATE compression, which is suitable for compressing memory footprints. While other compression algorithms that are optimized for performance (e.g., Snappy, zstd, LZ4) can compress memory faster, they typically result in much lower compression ratios, which is critical for microVM snapshotting. Their software implementations increase the amount of CPU resources required for making snapshots, especially when configured for more aggressive compression [1]. At the same time, hardware-accelerated DEFLATE yields high compression ratios as well as high speed, while requiring no CPU cycles for (de)compression. It should also be noted that hardware accelerators for other compression algorithms are also feasible [16, 26, 60] but not yet implemented in mainstream datacenter processors at scale.

IAA and other similar accelerators are designed for cloud environments. They are typically implemented as on-chip near-memory PCIe components, which allows them to be easily integrated with cloud services. For instance, IAA can run entirely in user space, it operates transparently over the application's virtual memory and can be virtualized through standard technologies, such as S-IOV [8]. All this makes IAA attractive for microVM memory snapshotting and prefetching. In this work, we explore this direction.

We first characterize the capabilities of IAA when it comes to compressing memory pages. Based on this characterization, we design Sabre, a memory prefetching system for microVMs built using IAA. Finally, we show how our memory prefetching unit integrates with serverless microVMs and evaluate its impact on end-to-end serverless benchmarks.

## 3 In-Memory Analytic Accelerator: Overview, Characterization, Insights

We now present an overview and characterization of the Intel In-Memory Analytic Accelerator (IAA) [6] using a set of diverse benchmarks [15]. This work mainly focuses on the compression/decompression capabilities of the accelerator. However, given that other capabilities share the same IAA frontend pipeline, interfaces, and software semantics, most of our findings also apply to these other domains. To our knowledge, this is the first publicly available characterization of the IAA hardware. The insights from this characterization are used to derive the design of Sabre, described in Section 4.

Note that given the diverse set of execution models, configurations, workloads, and variations of IAA hardware in different SKUs, it may be possible to achieve even higher performance compared to what we showcase in our characterization. Specifically, benchmarks designed specifically to stress test the accelerator may be able to improve IAA's performance further. For the purpose of this paper, we only benchmark the accelerator with a set of scenarios required to give comprehensive insights into using in-memory compression techniques in serverlerss microVMs and to derive the design of Sabre.

### 3.1 Overview of the IAA

Intel's IAA is a hardware accelerator first introduced in Intel's 4<sup>th</sup> Gen Xeon Scalable Processors (code-named Sapphire Rapids) [12] to speed up data processing across application classes. It was designed with the primary use case being databases and query processing systems [7]. The accelerator physically resides in the uncore part of the processor's SoC near the memory controller and Last Level Cache. A single CPU can accommodate multiple IAA devices on its SoC.

The IAA accelerators are logically integrated as PCIe devices and exposed to the host as a single root complex integrated endpoint. This is set up to enable transparent integration of the accelerators with software. IAA features scalability, full virtualization support via PCIe S-IOV, Shared Virtual Memory support (SVM or SVA as defined by Linux kernel documentation) [11], and transparent user-space interaction with applications via a new ISA extension, called *ENQCMD*.

Communication and job submission to the accelerator are handled via *Work Queues* (WQs), similar to another emerging hardware – Data Streaming Accelerator (DSA) [48]. For this, software needs to create *descriptors* and *completions* allocated anywhere in the application virtual address space. Descriptors contain information describing the jobs assigned

to the accelerator's *Processing Units* (PEs), such as the locations of the source and destination buffers, opcodes, and operational and memory policy flags. Descriptors are submitted to the accelerator via the ENQCMD instruction directly from user space, which writes them into the device's memorymapped I/O (MMIO) registers. Upon receiving descriptors, the PEs fetch data based on the pointers in the descriptors. This is done through SVM which enables transparent sharing of the application's virtual memory with accelerators. When a PE finishes processing, it writes the corresponding completion record with the status information. The software can poll the completion records to identify the termination of tasks and any error information. If some application memory pages associated with data buffers are not available, the accelerator can request them via either Page Request Service (PRS) or through userspace page fault handling. In the latter case, software applications can resolve the page faults in a more suitable for a particular usage scenario way (e.g., by requesting pages from, for example, the network) in the user space.

IAA's job submission mechanism enables asynchronous/non-blocking and out-of-order processing of descriptors. The current hardware permits a large number of in-flight requests, which can be submitted from different threads and processes/tenants. The micro-architectural pipeline of the IAA hardware contains multiple PEs that can execute jobs concurrently. The DSA specification [4] and in-depth characterization [48] contain more details since both accelerators share the same specification for this part.

The IAA hardware contains PEs implementing different processing capabilities. These include encryption, compression, CRC offload, data filtering, scanning, extraction, selection, and expansion [5] (Table 3-1). Due to the scope of this work, we only focus on characterizing the (de)compression capability of IAA. IAA performs DEFLATE [30] compression, as defined in RFC 1951. DEFLATE is based on LZ77 matching and Huffman encoding. LZ77 matching eliminates redundancy by replacing repeated occurrences of substrings with references to a single version of the substring. This is a computationally intensive process making software implementations slow. The Huffman coder further deflates data by re-encoding the most common symbols with fewer bits using statistics of data distribution in the input stream. Internally, the IAA compression unit operates in three modes.

In the first – *Huffman-mode*, IAA performs hardware-accelerated LZ77 dictionary coding, using 4 KB windows, and encodes the results with pre-defined static Huffman tables. The second IAA mode – *Statistics-mode* is designed to sample input streams and construct the statistical data distribution to optimize Huffman tables for a particular input. Compression with input-specific Huffman tables usually allows much higher compression ratios. In Statistics-mode, IAA only constructs the histogram of the distribution of Huffman codes, but it does not write the actual Huffman tables yet. The latter

| Style   | Description                                                                                                  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------|--|--|

| Fixed   | Standard static DEFLATE; based on Huffman-mode with standard Huffman tables; enables faster                  |  |  |

| Block   | compression, but under general Huffman tables, which usually results in low compression ratios.              |  |  |

| Static  | Similar to Fixed Block, but using user-defined Huffman tables; can result in good compression ratios if the  |  |  |

| Block   | application is able to provide Huffman tables fitting all inputs well.                                       |  |  |

| Dynamic | Standard dynamic DEFLATE; two-phase compression with Statistics-mode followed by Huffman-mode;               |  |  |

| Block   | enables optimal Huffman tables per block and a better compression ratio, but requires more time to compress. |  |  |

| Canned  | Allows sharing the same Huffman tables between multiple blocks of compressed data; this is important when    |  |  |

|         | compressing many small scattered chunks to avoid having to keep/access Huffman tables per block.             |  |  |

Table 1: End-to-end compression styles supported in Intel IAA.

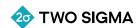

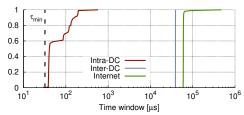

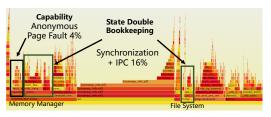

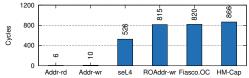

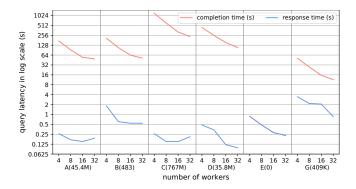

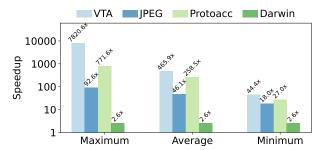

Figure 1: Comparison of software- and hardware-based DEFLATE compression for different datasets (sorted by uncompressed size) from Silesia Corpus and serverless VM snapshots (last two); the numbers denote speed-up of the hardware execution; a single IAA device with a single PE (engine) in blocking/synchronous mode is used; the software baseline runs on a single thread.

is done in the third mode - Huffman-Generation mode, which is only supported in some IAA implementations.

Based on these modes, IAA defines four main styles of compression (Table 1), and it is up to the control plane software to implement them. To make end-to-end (de)compression easier to implement, Intel has recently released the Query Processing Library (QPL) [7], which abstracts away the IAA modes and allows users to express compression in any of the supported modes. We next show the results of microbenchmarking IAA with different modes and implementations.

#### 3.2 **Characterizing Compression Using IAA**

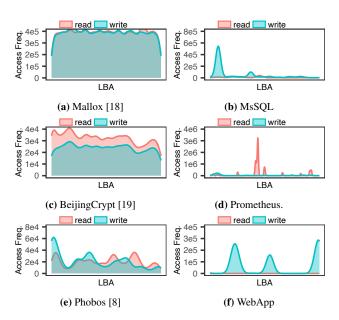

We characterize IAA (de)compression with a set of benchmarks written using the Intel QPL library v1.3.1. As input data, we use 11 datasets from the standard Silesia Corpus [29]; a common way to evaluate (de)compression. We also add two more datasets specific to our use case representing the dirty memory snapshots of microVMs. The snapshots were

obtained during request execution for two serverless applications from vSwarm [66] and FunctionBench [44,45]: a Python gRPC server (pythongrpc) and the Pillow image processing library (pillow). Both datasets only contain dirty pages of guest memory. Table 2 shows the specification of our testbed. At the time of writing, we had access to two Sapphire Rapids systems (SKUs) with slightly different configurations. We use the most recent production-grade SKU (Server #2 in Table 2) in all experiments unless otherwise noted.

## 3.2.1 Benchmarking IAA: Core Compute

We start with the characterization of the in-memory core computing capability of IAA. We assume that data is always available in memory, both for the source and destination buffers. We ensure that memories are initialized and touched to avoid page faults. This is important as page fault handling affects the accelerator's performance, and therefore we evaluate it separately. For all experiments in this section, we use a single

| CPU<br>(Server #1) | Intel 4 <sup>th</sup> Gen Xeon Scalable Processor;<br>2 NUMA nodes, 56 cores/112 threads;<br>Core/Uncore frequency (GHz): 1.7/ 1.8;<br>LLC capacity (MB): 110<br>IAA devices: 8 (4 per NUMA node)                          |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU<br>(Server #2) | Intel(R) Xeon(R) Gold 6438Y+; 2 NUMA nodes, 32 cores/64 threads; Core/Uncore frequency (GHz): 2.3/ 1.8; LLC capacity (MB): 60 IAA devices: 2 (1 per NUMA node)                                                             |  |

| IAA                | available PEs per device: 8 capabilities (as per GENCAP register): - Huffman generation mode: disabled; - Page Request Service (PRS): enabled; - Block-on-Fault: enabled; WQ configuration: shared, 8 per device, size: 32 |  |

| Memory             |                                                                                                                                                                                                                            |  |

| Disk               | Intel SSDSC2KG960G8 Sequential O_DIRECT read bandwidth (MB/s): 550                                                                                                                                                         |  |

| Host OS            | Ubuntu 22.04;<br>Kernel: 5.15, patched with [9] to enable ENQCMD;<br>Kernel boot arguments: <i>intel_iommu = on,sm_on</i>                                                                                                  |  |

| Guest OS           | Rootfs: Debian GNU/Linux 12 (bookworm)                                                                                                                                                                                     |  |

| (Section 5)        | Kernel: 4.14.174                                                                                                                                                                                                           |  |

| IAA stack          | Driver: idxd<br>Middleware: Intel QPL v1.3.1                                                                                                                                                                               |  |

Table 2: Testbed hardware and software configuration.

IAA device configured with a single PE (engine); we submit the jobs to the accelerator from a single CPU thread in the blocking/synchronous mode and wait till completion by polling associated completion records. The software baseline runs on a single CPU core.

We first compare the performance and compression ratios of IAA-enabled compression and its software implementation in QPL. Since the IAA hardware does not allow explicitly selecting compression levels (compression levels are subjective and vary across implementations), we set the default compression level-1, as defined by QPL, for the corresponding software implementation. Since our version of IAA does not offload Huffman table generation, the hardware implementation of dynamic DEFLATE compression is actually hybrid: statistics collection, LZ77 encoding, and compressed stream generation run in hardware, while Huffman table generation runs in software. The hybrid operations run on a single CPU core. Figure 1 shows the compression results.

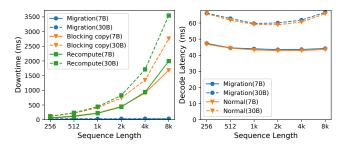

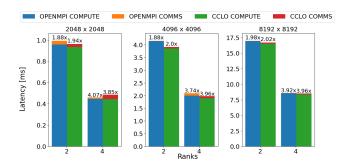

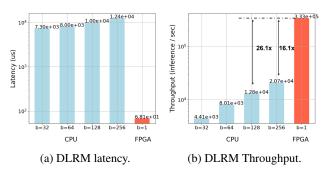

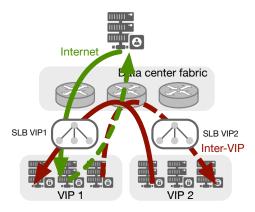

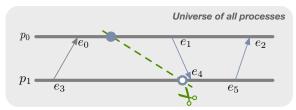

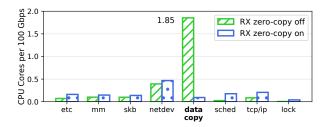

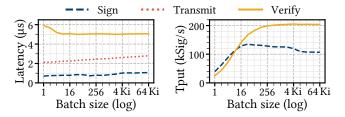

The hardware implementation always overperforms software in compression time. The difference reaches  $6.1 \times$  and  $13.5 \times$  for dynamic and fixed compression, respectively. In our datasets of dirty memory snapshots, the speedup reaches  $9 \times$ . The achieved compression ratios for software and hardware executions are similar. Figure 2 shows the performance of decompression. We only show the decompression of *dynamic* streams, as in these datasets, decompression performance does not depend on the compression mode. In all cases, IAA decompresses an order of magnitude faster than software.

Note that in this paper, our experiments only compare IAA to the software implementation of the same DEFLATE al-

gorithm. To compare against many other software compression algorithms (e.g., Snappy, zstd, LZ4, etc.), please refer to the publicly available in-memory benchmarks based on the Silesia Corpus (for example, Izbench [1]). The *synchronous* throughput of IAA's (de)compression can be obtained from Figures 1 and 2 based on the size of the datasets. For example, the fixed-DEFLATE compression on the *nci* dataset reaches 1800 *MB/s*, and its decompression - 4600 *MB/s* on a single engine. These numbers are expected to be lower than the *asynchronous* streaming (de)compression (using the non-blocking mode of IAA) which we do not characterize in this paper.

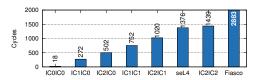

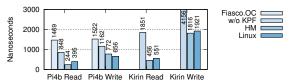

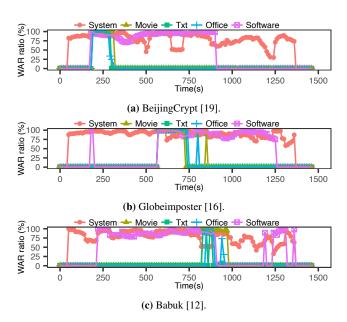

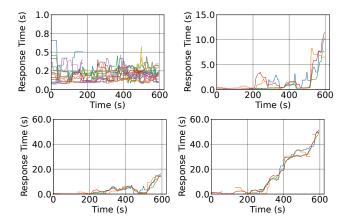

We then profile (Figure 3) IAA's (de)compression for many small 4 KB sized chunks for the same datasets. As previously mentioned, the Canned-which is essentially a Static Block—mode allows sharing Huffman tables between data chunks, therefore reducing both the space and processing time when data is scattered over many small blocks. This is very useful when compressing individual memory pages. In Figure 3, the first group of bars shows the baseline compression using Dynamic Block over a continuous region. We then break it into 4 KB chunks and compress them naïvely, with the Dynamic Block, independently for each chunk. As a result, compression time explodes due to processing tables separately; the decompression time also suffers, as the Huffman tables need to be parsed. The Canned operation reduces the overhead of scattered compression. Most interestingly, it enables fast decompression of scattered data, which is only marginally higher than the continuous baseline.

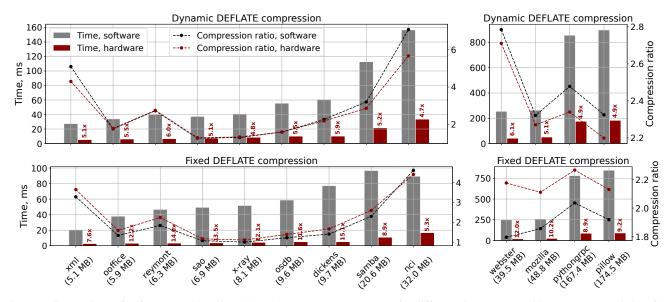

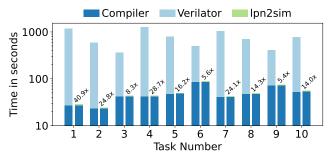

Figure 4: Latency of single-thread *synchronous* (de)compression with parallel *hardware* execution on 4 IAA devices with 8 engines each; only two benchmarks are shown for brevity.

## 3.2.2 Benchmarking IAA: System Integration

We now characterize the IAA hardware together with systemlevel aspects. We use the same datasets and setup as before.

We first evaluate how job parallelization within the IAA PEs may further speed up (de)compression. Given that our earlier SKU has more IAA engines/PEs (refer to Table 2), we use *Server #1* in this experiment. Note that at the time of writing, the QPL library did not allow crossing NUMA boundaries between the data and IAA devices. Therefore, only 4 IAA devices (32 PEs/engines in total) are utilized at most for this experiment.

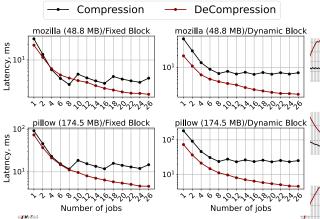

There are two main ways to leverage parallelism within the IAA: with synchronous and asynchronous job submission. In the first case, a large chunk of data can be split into multiple smaller blocks, and these blocks are then submitted to multiple available PEs. The software then blocks and waits until all PEs finish processing. This allows us to reduce the time/latency of a single (de)compression job. In the asynchronous case, a *stream* of multiple blocks from potentially different dataflows/threads is supplied into the accelerator without waiting for the completion of the previous blocks, therefore utilizing the hardware at maximum capacity. This yields the highest IAA utilization and throughput. For fast microVM restoration, the only performance metric that matters is how fast the system can decompress a single snapshot from a single CPU thread into the microVM guest memory. We therefore only benchmark the synchronous job parallelization in this paper.

We implement parallel synchronous processing via the *non-blocking synchronous* descriptor submission. Here multiple descriptors are submitted at the same time from a single CPU thread without waiting for immediate completion of individual descriptors. Figure 4 shows that for a hardware concurrency of up to 8 compression jobs, the latency reduction

reaches  $4-7\times$  with respect to sequential execution. Dynamic Block compression scales worse due to the software overhead of Huffman table creation. *Decompression* scales up to 26 jobs, reaching  $17\times$  latency reduction for the *pillow* dataset. These results demonstrate how multiple IAA engines can be used to achieve even lower (de)compression latency.

Until now, we have only tested the behavior of IAA when processing in-memory data, which was the majority of initial use cases for the accelerator. In-memory operation is achieved when source and destination buffers are present both in the memory and page table of the calling process. This holds when, e.g., streaming over the same buffers. However, in certain cases, data is not entirely present in memory, e.g., when processing inputs from a file or into newly allocated memory. In these cases, the accelerator must resolve page faults.

The fundamental source of page faults in systems such as IAA and DSA is the fact that they operate directly on the application's virtual address spaces via SVM [11]. As a result, similarly to CPU processing, when a page requested by the accelerator is not found in the page table, a major or minor page fault occurs. The result of the page fault handling (e.g., the translation) is then cached in the accelerator's Address Translation Service (ATS). When the translation is available in the CPU/kernel, the page fault does not happen, but the ATS must fetch the translation from the host via a translation fetch request. We now benchmark IAA in the case of page faults and translation fetch requests. We use standard 4 KB pages and an SSD disk with 550 MB/s of provisioned sequential read bandwidth. For compression, we use a single-pass Fixed Block to avoid the side effects of hybrid two-phase operations.

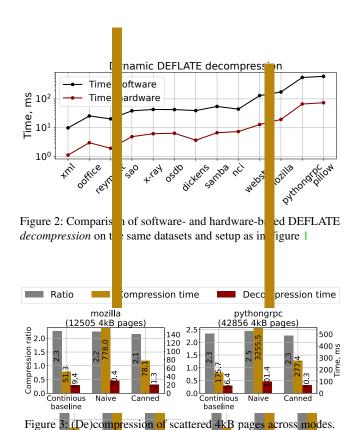

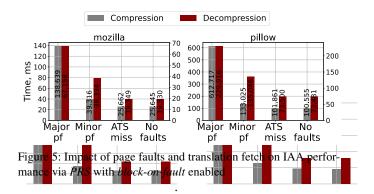

IAA supports two modes to handle page faults: via hardware-initiated on-demand paging via PRS or in user space with custom application-defined page fault handlers. The mode is controlled via the work queue configuration or through the PCIe device configuration if the former is not available. When PRS is enabled, the hardware can request up to *N* (specified in *PRSREQCAP* register) pages from the host concurrently. The actual page fault handling is done by the kernel through IOMMU interrupts. Figure 5 shows the time required to process descriptors in case of different hardware-

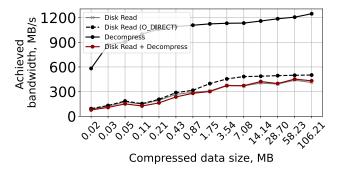

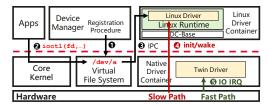

Figure 6: Single-job, single-engine, synchronous decompression bandwidth when reading disk inputs via PRS with block-on-fault enabled.

initiated page faults. We benchmark the worst-case scenario when the entire dataset causes page faults (12492 pages for *mozila* and 44672 pages for *pillow*). As expected, major page faults have a severe impact on the accelerator's performance. The impact of minor page faults is lower, but still  $\approx 2 \times$  for decompression. The ATS translation fetch has the smallest impact of  $\approx 20~us$  across all pages. In general, decompression is more sensitive to page faults than compression; this is because the former is less compute-bounded.

Finally, we characterize the achieved decompression bandwidth when reading input data from an SSD (Figure 6), which is critical for our memory restoration use case. The dashed black and gray lines show achieved sequential disk read bandwidth with and without *direct I/O* (O\_DIRECT). Direct I/O allows bypassing the page cache when reading files from the disk. In certain cases, this helps to reach the highest bandwidth of I/O operations. The solid black line shows the achievable bandwidth of a single-job synchronous decompression over data in memory, and the red line when reading input from the disk via hardware on-demand paging (i.e., via PRS). The latter is achieved through shared mapping of the input file into the IAA buffers and enforcing sequential I/O using *posix\_fadvise*.

IAA decompression is a *streaming* operation, and it always accesses input buffers sequentially. In an ideal system, the decompression phase will completely overlap with the operation fetching data from the disk. Hence, the achieved end-to-end throughput will be decided by the slower operation - be it decompression or disk I/O. As Figure 6 shows, with default hardware on-demand paging, the achieved endto-end bandwidth is the same as disk read without direct I/O. This demonstrates that IAA streaming processing can entirely overlap with disk I/O. It is 10-15% lower, however, than the achievable bandwidth of reads with direct I/O, because IAA communicates with the disk via the OS page cache when running over PRS. A way to further improve IAA over data from disk is to replace PRS with application-specific page fault handling. However, in that case, the end-to-end behavior depends on whether IAA is configured with enabled block-on-fault, a feature that allows the accelerator to block and wait until data becomes available. Without block-on-fault, IAA terminates

with partial completion and cannot continue decompression from the place where it stopped; as a result, the job needs to restart from scratch. Given the streaming nature of IAA, it is possible to entirely close the gap between direct disk I/O and decompression by using block-on-fault in combination with O\_DIRECT reads in a custom page service handler, either in a driver or user space. We leave this to future work.

## 4 Sabre Design

## 4.1 Memory Prefetching Accelerator

We use the insights from the characterization study of Section 3 to design Sabre. Sabre is a hardware-accelerated memory snapshotting and restoration system for microVMs that is agnostic to the underlying algorithm used to identify dirty pages and create VM snapshots.

Sabre is designed to efficiently compress the guest VM physical pages to create snapshots, such that they can be decompressed (and mapped) quickly when restoring the snapshot upon a function invocation resulting in a cold start. As an input, Sabre accepts a vector of addresses for each of the guest physical memory pages which need to be placed in the snapshot, according to the underlying dirty page selection mechanism. It then compresses pages using IAA and writes them in a file. During the VM restoration process, Sabre uses fast IAA decompression in combination with efficient sequential disk I/O to quickly fetch the pages from the snapshot, decompress, and install them in the target VM's physical memory. The main goal of Sabre is to hide the decompression latency as much as possible behind the disk I/O and page fault handling (when mapping pages) such that the overhead of decompression is minimized. This is possible to achieve given the streaming nature of IAA decompression.

Sabre shows that irrespective of the method used to identify dirty pages and create VM snapshots, hardware-accelerated compression, and restoration can have a significant impact on performance. In the simplest case, dirty pages can be identified by the page tracking mechanism in the VMM (e.g., Firecracker's *Diff* snapshots); in more complicated cases, custom algorithms can be used (e.g., different working set estimation techniques [64,72]).

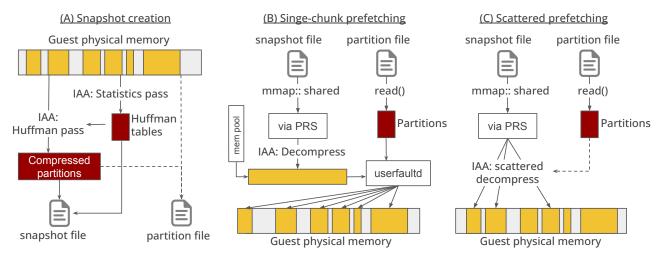

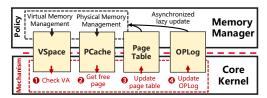

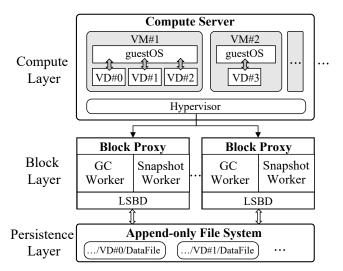

Figure 7-A shows an overview of Sabre's snapshot creation pipeline along with two designs for memory prefetching, both of which are used by Sabre under different scenarios.

**Snapshot creation:** We first describe our snapshot creation process, which is based on two observations. First, creating a snapshot is outside of the VM restoration's critical path, so the objective is selecting the compression algorithm that achieves the highest compression ratio, which as we showed in Section 3 is dynamic DEFLATE. Second, since the VM dirty pages are distributed in a non-contiguous manner across the guest's physical memory space, the (de)compressor should operate over separate (often small) chunks of memory. As

Figure 7: High-level overview of snapshotting with Sabre.

Figure 3 shows, the "Canned" style compression works best in this case: it enables implementing static DEFLATE with pre-computed Huffman tables, which closely resembles the efficiency of Dynamic DEFLATE. Sabre's snapshot creation process first runs IAA in Statistics mode to sample the statistical distribution of data in all dirty pages and create appropriate Huffman tables. It then compresses the scattered regions of dirty pages with these Huffman tables. The resulting compression stream alongside the Huffman tables is written into the snapshot file. For experimentation reasons, we also enable using Dynamic DEFLATE as well. In addition to the snapshot file itself, Sabre also writes the partition file containing the "schema" of the dirty pages, i.e., the offsets and original/compressed sizes of each partition.

**Memory prefetching:** The memory prefetching process is more complicated to engineer as it is on the critical path of VM restoration, and therefore needs to be carefully optimized. The main trade-off Sabre must navigate is balancing the desire to handle all partitions of dirty pages as a single contiguous memory region and the cost that comes with that.

Handling all partitions of dirty pages as a single continuous memory region is better for the accelerator, as continuous DMA is more efficient than scattered DMA, and it is also better for the PRS and disk I/O, as the underlying PRS-initiated page faults are sequential. The latter works well with sequential disk reads, therefore yielding the best utilization in terms of disk bandwidth. However, continuous decompressed partitions need to be placed by the same addresses in the guest VM physical memory as in the original VM when the snapshot was taken. Sabre implements it using userfaultfd, which comes at the cost of memory copy.

We implement this approach in Sabre's single-chunk memory prefetching shown in Figure 7-B. To reduce the overhead of allocating the decompression buffers, Sabre can optionally use a pre-allocated memory pool for the buffer for the time of decompression. The size of the pool is bounded by the

sum of the sizes of dirty pages of the VMs currently restored simultaneously. This space is reusable across different restoration processes and therefore does not consume much memory. However, users of Sabre can always disable the memory pool (at  $\approx 10\%$  cost of memory restoration) if the pool's impact on the memory density is an important concern. Sabre's memory prefetching relies heavily on the PRS hardware mechanism to bring snapshots from the disk. This is achieved by running IAA against a shared not pre-faulted (i.e. the actual file I/O gets initiated by PRS) mapping of the snapshot file. As Figure 6 shows, default PRS is near-optimal at handling IAA inputs from the disk, and it allows hiding the decompression time by overlapping it with the disk I/O. In most cases, the difference with sequential disk read bandwidth is marginal. We confirm that running IAA over pre-faulted or pre-fetched (via read) snapshot files is much slower than via PRS.

To address the high cost of partition placement when treating the entire memory region as contiguous, Sabre also implements memory prefetching based on scattered IAA decompression (Figure 7-C). Here, Sabre directly DMAs decompressed partitions into the right locations in the guest's physical memory, while still handling inputs from disk via PRS. This allows the system to bypass page installation, however, it makes the IAA hardware less efficient due to the large number of scattered DMAs and the bookkeeping of the corresponding descriptors (the current implementation of IAA does not allow chaining and batching of descriptors, so each one must be submitted separately by software). In addition, splitting the decompression stream into multiple jobs hurts the efficiency of PRS at reading data from the disk, which further slows down memory prefetching. The latter can be addressed by implementing a custom user-space page fault handler, as discussed in Section 3.

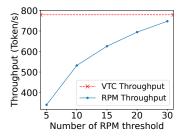

In both designs for memory prefetching, IAA decompression can be done using a single IAA job/engine or parallelized across all available engines. This is implemented via nonblocking job submission with a rotating pool of descriptors. In this mode, Sabre attempts to submit N decompression jobs at the same time, where N is the desired concurrency degree or the number of available free engines (whichever is smaller). Upon asynchronous out-of-order completion, the corresponding descriptors are returned to the pool for later reuse. This enables a streaming operation for Sabre's decompression when multiple engines are used. Note that a single IAA engine in blocking synchronous mode is capable of achieving  $\approx 1.2 \ GB/s$  at decompressing our snapshot datasets. Since this is higher than our disk read bandwidth, we always use a single IAA job in all remarking experiments, unless otherwise noted.

The exact operation of the memory prefetching unit, such as the choice of the restoration design (between single-chunk and scattered), the compression style (dynamic or static DE-FLATE) for snapshot creation, the number of concurrent decompression jobs, etc. are configured by Sabre during runtime. The desired configuration can be selected differently for each microVM's snapshotting/restoration call. Next, we microbenchmark our memory prefetching unit under different configurations and types of snapshots.

## 4.2 Microbenchmarking Memory Restoration

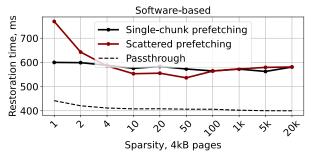

We now analyze the two design options for memory prefetching shown in Figure 7 using a dataset of microVM dirty memory snapshots with different sparsities. We create synthetic datasets from the *pillow* snapshot (Section 3) that range from *most scattered*, when each page is separated, to a case with few large contiguous regions of dirty pages. In practice, the pattern depends on the underlying mechanism used to identify snapshot pages and the applications running in the VMs.