# SoK: Where's the "up"?! A Comprehensive (bottom-up) Study on the Security of Arm Cortex-M Systems

Xi Tan and Zheyuan Ma, CactiLab, University at Buffalo; Sandro Pinto, Universidade do Minho; Le Guan, University of Georgia; Ning Zhang, Washington University in St. Louis; Jun Xu, The University of Utah; Zhiqiang Lin, Ohio State University; Hongxin Hu, University at Buffalo; Ziming Zhao, CactiLab, University at Buffalo

https://www.usenix.org/conference/woot24/presentation/tan

## This paper is included in the Proceedings of the 18th USENIX WOOT Conference on Offensive Technologies.

August 12-13, 2024 • Philadelphia, PA, USA

ISBN 978-1-939133-43-4

Open access to the Proceedings of the 18th USENIX WOOT Conference on Offensive Technologies is sponsored by USENIX.

## SoK: Where's the "up"?! A Comprehensive (bottom-up) Study on the Security of Arm Cortex-M Systems

Xi Tan CactiLab, University at Buffalo Zheyuan Ma CactiLab, University at Buffalo Sandro Pinto

Universidade do Minho

Le Guan *University of Georgia*

Ning Zhang

Washington University in St. Louis

Jun Xu University of Utah

Zhiqiang Lin

Ohio State University

Hongxin Hu University at Buffalo Ziming Zhao CactiLab, University at Buffalo

#### **Abstract**

Arm Cortex-M processors are the most widely used 32-bit microcontrollers among embedded and Internet-of-Things devices. Despite the widespread usage, there has been little effort in summarizing their hardware security features, characterizing the limitations and vulnerabilities of their hardware and software stack, and systematizing the research on securing these systems. The goals and contributions of this paper are multi-fold. First, we analyze the hardware security limitations and issues of Cortex-M systems. Second, we conducted a deep study of the software stack designed for Cortex-M and revealed its limitations, which is accompanied by an empirical analysis of 1,797 real-world firmware. Third, we categorize the reported bugs in Cortex-M software systems. Finally, we systematize the efforts that aim at securing Cortex-M systems and evaluate them in terms of the protections they offer, runtime performance, required hardware features, etc. Based on the insights, we develop a set of recommendations for the research community and MCU software developers.

#### 1 Introduction

Microcontroller units (MCUs) are small computers designed for embedded and Internet of Things (IoT) applications in contrast to microprocessors used in smartphones, personal computers, and servers. They operate at frequencies ranging from several kHz to several hundred MHz. The sizes of their ROMs and RAMs are small and usually fall into the range of several hundred bytes to several megabytes. Even though MCUs are general-purpose computers, they are commonly employed for running specialized software and firmware tailored to specific applications.

The Arm Cortex-M family, which has three major architectures and 12 processors as of 2023, is the most popular 32-bit MCU architecture without a memory management unit (MMU) on the market. More than 80 hardware vendors have licensed Cortex-M cores [1]. 4.4 billion Cortex-M MCUs were shipped in the 4th quarter of 2020 alone [2], and it is es-

timated that Cortex-M MCUs account for almost 100 billion deployed embedded and IoT devices in 2021 [3].

Given the sheer volume of deployed Cortex-M systems, one would anticipate that the security of their hardware and software stack has been thoroughly studied and systematized. Unfortunately, this is not the case. To bridge the knowledge gap that hinders the users and researchers, we seek to answer the following questions regarding their security states:

• Q1 - What are the security features, limitations, and issues at the Cortex-M microarchitecture, instruction set architecture (ISA), and beyond? The answer helps understand the constraints in securing software on Cortex-M.

To address this question, we analyze the hardware security limitations of Cortex-M by comparing its offerings with microprocessors. Our main observation (§3) is that Cortex-M processors lack support for memory virtualization and provide only basic memory protection mechanisms. Additionally, their other security features, e.g., TrustZone, are streamlined compared to their Cortex-A counterparts and introduce new vulnerabilities.

• Q2 - What are the security mechanisms and flaws of Cortex-M based software systems? The answer helps understand the status of Cortex-M software security in real-world systems.

To answer this question, we compile a dataset of 1,797 realworld Cortex-M firmware samples, including 1,003 newly collected ones, and perform by far the largest empirical analysis on the adoption of security mechanisms on real-world Cortex-M systems. In particular, we summarize the software architectures found in these samples and other research projects. We develop binary analysis tools to verify if the collected samples leverage the security mechanisms that have been widely deployed on microprocessor-based systems, e.g., privilege separation and stack canaries. We uncovered that (§4) despite extensive research on more secure architectures for microcontroller-based systems, these advancements are rarely implemented in real-world firmware. Moreover, the hardware security features offered by Cortex-M processors are seldom utilized in the majority of the assessed firmware; hence, where is the "up"?!. Furthermore, existing compiler-based mitiga-

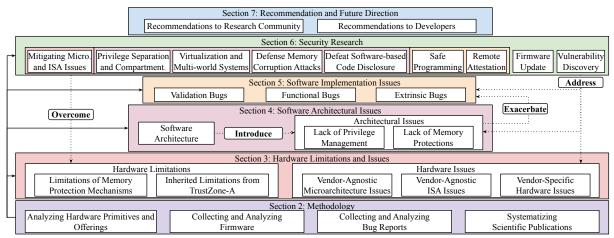

Figure 1: Overview of the organization and contributions of this paper

tions designed for process-based operating systems (e.g., stack canaries) prove ineffective when operating within a single physical address space.

• Q3 - What are the nature and severity of the publicly disclosed vulnerabilities in the Cortex-M based software systems? The answer helps find out software bugs that are more likely to be exploited in such systems.

To tackle this question, we analyze 310 Cortex-M related software bug reports spanning nearly six years, from 2017 until 2023. Our analysis includes systems developed by nine hardware vendors, e.g., Nordic and NXP, and seven real-time operating systems (RTOS), e.g., FreeRTOS. We further categorize the software implementation issues into validation, functional, and extrinsic bugs, a taxonomy adopted in a recent work studying the vulnerabilities in Cortex-A systems [4]. Our insights (§5) include that these systems not only exhibit memory corruption vulnerabilities but also display weaknesses in their protocol and cryptographic implementations.

Q4 - What defenses for Cortex-M systems have been explored in the literature, and what are their limitations?

Together with the previous answers, this helps shed light on new research directions to secure Cortex-M systems.

To address this question, we create a taxonomy and comparative evaluation of over 50 papers spanning nearly nine years. Our evaluation framework considers the defenses each solution offers, the hardware units it relies on, and their runtime overhead in terms of memory size, performance, etc. Our major observations (§6) include the research community not only shifts the exact same defenses from microprocessor-based systems on Cortex-M systems, e.g., enforcing isolation and confinement, stack integrity, and control flow integrity, but also develops solutions intrinsically linked to the MCU characteristics, e.g., peripheral-oriented fuzzing.

Based on the insights, we develop a set of recommendations for the research community and MCU software developers (§7). Figure 1 provides an overview of the organization and contributions of this paper. We have open-sourced our source

code, dataset, and supplementary materials <sup>1</sup>.

## 2 Methodology

#### 2.1 Adversarial Model

In general, we consider the security limitations and issues of the microarchitecture, ISA, and above. In particular, we assume an adversary can perform (i) microarchitecture sidechannel attacks, e.g., bus interconnect; (ii) glitching, e.g., voltage fault injection; (iii) remote attacks via a network; (iv) nearby wireless attacks via BLE, ZigBee, etc.; (v) local attacks through peripherals and debug ports; and (vi) software side-channel attacks. On systems without TrustZone-M, we consider an adversary with one or more of the following objectives: (i) to obtain secrets from the flash, e.g., intellectual property (IP) theft and RAM; (ii) to tamper sensitive data; (iii) code execution and privilege escalation, e.g., control-flow hijacking. On systems with TrustZone-M, we assume all components in the non-secure state are untrusted and consider an adversary with all aforementioned goals as well as compromising the secure state.

#### 2.2 Analyzing Hardware Offerings

We provide a detailed analysis of the hardware security limitations and issues. Due to the page limit, a detailed walkthrough of the Cortex-M architecture is not included in this paper. Interested readers please refer to our supplementary materials, which consolidate information from various official sources [5–14]. To aid in research for the community, we have developed an open-source code suite, demonstrating the use of Cortex-M security features.

#### 2.3 Collecting and Analyzing Firmware

**Collecting Firmware**. The process of collecting and decoding Cortex-M firmware was far from straightforward and re-

<sup>&</sup>lt;sup>1</sup>https://github.com/CactiLab/SoK-Cortex-M

Table 1: Manufacturer distribution of the compiled real-world firmware dataset. Italic represents newly collected sample that were not publicly released before.

| HW Vendor  | Nordic<br>[15] | Other<br>Nordic | TI<br>[15] | Telink | Dialog | NXP | Cypress | ST<br>[16] | Total |

|------------|----------------|-----------------|------------|--------|--------|-----|---------|------------|-------|

| # Firmware | 768            | 690             | 22         | 192    | 53     | 1   | 67      | 4          | 1,797 |

| # Devices  | 513            | -               | 20         | 120    | 36     | 1   | -       | -          | 689   |

sulted in the accumulation of significant amounts of unusable data. We used three approaches to collect firmware: (i) we filtered Cortex-M firmware from publicly available embedded system datasets [15, 17–21]; (ii) adopting an analogous methodology as described in [15], we developed scripts to analyze/unpack mobile apps and extract potential Cortex-M firmware. Using this approach, we collected 4,693 potential samples from six silicon vendors. These samples are in various formats, e.g., S-record for NXP, cyacd format for Cypress, and proprietary format of Qualcomm; (iii) we crawled websites for 25 silicon and device vendors known for embedded and IoT devices. This effort resulted in 1,687 potential samples, but none of them turned out to be Cortex-M firmware. This aligns with the findings in FirmXRay [15], which noted that vendors seldom make their firmware available online.

As shown in Table 1, our firmware collection endeavor ended up with 1,797 unique Cortex-M firmware from seven hardware vendors. Among these, the FirmXRay dataset includes 790 firmware samples, representing 533 distinct devices from two vendors (768 from Nordic [22] and 22 from Texas Instruments [23]). Additionally, the HEAPSTER dataset [16] encompasses four Cortex-M binaries from STMicroelectronics (ST) [24]. Furthermore, we have gathered 1,003 firmware from other vendors, including Nordic (690), Telink [25] (192 firmware for 120 unique devices), Dialog [26] (53 firmware for 36 devices), NXP [27] (1), and Cypress [28] (67). These samples have not been publicly shared before. The firmware in our collection is in raw binary format, lacking symbolic information.

Analyzing Firmware. We used FirmXRay [15] to recognize the base address of each firmware. Scripts were then developed to identify the Cortex-M vector table and perform recursive disassembly with Ghidra [29]. We also applied scripts to filter a portion of firmware samples that contain device information, ensuring that they are from distinct devices. We conducted an analysis of the disassembled samples using the following heuristics: (i) to identify if firmware uses any RTOS, we performed binary function recognition [30] and string searches for ten popular RTOSs; (ii) for firmware that uses an RTOS, we analyzed if task stack overflow checks are performed. To this end, we checked if the task stack overflow handling functions, e.g., osRtxKernelErrorNotify() with the parameter osRtxErrorStackOverflow in CMSIS RTOS2 [31], are called by other functions in the firmware; (iii) we analyzed if and how the CONTROL register is changed and how the SVC instruction is used to determine privilege separation and stack usages; (iv) to check if there are stack

canaries, we analyzed function prologues and epilogues for specific instruction patterns derived from canary-protected functions generated by three compilers. In addition, we searched if the firmware has the hard-coded libc error message "\*\*\* stack smashing detected \*\*\*" and whether the function printing out this message is called by other functions, which is a practice used before [32].

#### 2.4 **Collecting and Analyzing Bug Reports**

We retrieved over 500 hardware and software bug reports related to Cortex-M systems from 2017 to 2023 [33], which shows a growing trend. Besides "Arm", we included in our list of keywords the names of top hardware vendors [34], popular RTOSs [35], and embedded SSL libraries, e.g., Mbed TLS [36] and wolfSSL [37]). We manually confirmed the bug reports indeed affect Cortex-M systems, including verifying the affected chips and inspecting the source code. Two researchers worked together to categorize each bug into a relevant subclass, which was verified by a third researcher.

## 2.5 Systematizing Scientific Publications

We collected over 30 papers on Cortex-M security from top conferences<sup>2</sup>. In addition, we supplement our list of surveyed papers with another over 20 articles that are highly relevant to the topic but published in other venues. Note that our systematization focuses on the works explicitly designed for and implemented on Cortex-M. Nevertheless, we discuss related works that were designed for or implemented on other architectures but may be applied to Cortex-M in §6.10.

#### 2.6 Threats to Validity

Our analysis of firmware may be subject to biases and imprecision due to the limited number of firmware. There is a risk of over-representing systems from specific vendors. Most firmware in our dataset (57.3%) are raw binaries and lack detailed device and architecture information, making it difficult to confirm their intended use cases and resulting in a potential bias in analyzing similar firmware samples. Additionally, the lack of proof-of-concept exploits and vague CVE descriptions introduces imprecisions in the classification of vulnerabilities. Furthermore, our analysis focuses on publicly disclosed vulnerabilities. Undiscovered vulnerabilities could unveil additional fundamental issues in Cortex-M systems.

#### **Hardware Limitations and Issues**

#### **Hardware Limitations**

Hardware limitations are missing or constrained hardware security features, which are typically non-patchable. Compared

<sup>&</sup>lt;sup>2</sup>https://csrankings.org/

with Cortex-A, Cortex-M features distinct design elements, particularly in its memory protection mechanisms and the TrustZone extension (TrustZone-M versus TrustZone-A).

## Limitations of Memory Protection Mechanisms

- L01. No memory virtualization: No hardware-supported memory virtualization is available on Cortex-M due to the absence of a memory management unit (MMU). Instead, software modules share the same physical address space. Such lack of memory virtualization also implies a small address space (4GB), which presents challenges to effective address space layout randomization (ASLR) due to low entropy.

- L02. No input-output memory management unit: Besides MMU, input-output memory management unit (IOMMU) or its equivalents, i.e., IOMPU, that provide memory protection from malicious direct memory access (DMA)-capable peripherals are also missing on Cortex-M. Some hardware vendors implement their own IOMPU, i.e., the resource domain controller on NXP i.MX RT [38,39], but they are only found in some of the latest devices.

- L03. A small number of MPU regions and limited sizes: Cortex-M only supports a small number of memory protection unit (MPU) regions, and the size of regions must be a multiple of 32 bytes. Compared to the page-based memory access control on microprocessors, the granularity of MPU-based is coarse-grained, and it is insufficient to implement fine-grained isolation that requires a large number of regions.

- L04. A small number of secure/non-secure memory regions: The number of regions supported by secure attribute unit (SAU) is small, e.g., up to 8 regions on Cortex-M33, resulting in limited design choices in splitting the secure and non-secure address space. To alleviate this issue, silicon vendors use the implementation defined attribution unit (IDAU), which supports up to 256 regions, to create more partitions. However, if more than 256 partitions are needed or the device has many peripherals, this may not be enough [40].

#### Inherited Limitations from TrustZone-A

- L05. No intrinsic encryption to protect the secure state **memory:** TrustZone-M does not encrypt the secure state memory. Consequently, cold boot attacks [41] can dump the secure state memory. There could also be information leakage when a memory protection controller (MPC) assigns a memory region from the secure state to the non-secure state at run-time, which we will discuss in 105.

- L06. Lack of intrinsic support for multiple trusted execution environments: TrustZone-M only provides *one* isolated execution environment in which the trusted firmware executes, resulting in a large software trusted computing base (TCB). For instance, TF-M [42] has over 117K lines of code.

- L07. Lack of hardware-based remote attestation in **TrustZone-M:** Same as Cortex-A [4], Cortex-M TrustZone lacks a hardware-based integrity reporting mechanism, so it

cannot provide a hardware-based remote attestation as Intel software guard extensions (SGX) does. For example, the Arm platform security architecture (PSA) introduces a weakened software-based attestation method [43, 44].

#### **Insights**

- The Cortex-M architecture offers weaker memory management interfaces than popular microprocessors, creating challenges to enforce memory isolation and security.

- TrustZone-M inherits hardware limitations of TrustZone-A and introduces more constraints.

#### 3.2 Hardware Issues

Hardware issues discuss vulnerable hardware components and hardware-supported operations.

Vendor-Agnostic Microarchitecture Issues

I01. Vulnerable to microarchitectural side-channel attacks: Although most Cortex-M processors lack a cache or branch predictor at the microarchitectural level, there are other side channels that can leak information.

Information leakage through power analysis: ELMO [45] demonstrates the feasibility of reversing AES S-Box output code sequences through power analysis on the Cortex-M0 processor. Furthermore, Vafa et al. [46] successfully applied a power analysis attack to recover running instructions on the Cortex-M3 processor.

Information leakage through timing side-channels: MCU bus interconnect arbitration logic involves delays when multiple bus masters, such as the CPU and DMA, simultaneously access a shared secondary port, like a memory controller. As demonstrated in BUSted [47], the attacker can successfully bypass protections provided by the MPU and TrustZone by exploiting these timing differences.

Information leakage through long-term data remanence: UnTrustZone [48] reveals that static random-access memory (SRAM) can be manipulated to imprint and expose on-chip secrets by accelerating analog-domain changes in SRAM. Using this method, UnTrustZone successfully extracts AES keys and proprietary firmware from various Cortex-M devices protected by TrustZone.

**I02. Vulnerable to fault injections:** A fault injection attack involves deliberately causing errors in a system's hardware (e.g., voltage, clock, electromagnetic) to disrupt its normal operations of a digital circuit and exploit these induced faults for malicious purposes. Johannes Obermaier and Marc Schink et al. discussed how to escalate the debug interface permissions or execute arbitrary code by injecting faults into voltage [49], Quad-SPI bus [50], and electromagnetic [51] at boot time on Cortex-M0/3/4 devices.  $\mu$ -Glitch [52] entails injecting multiple, coordinated voltage faults into Cortex-M devices to bypass the TrustZone protection, allowing leaking secrets stored in secure memory into non-secure code.

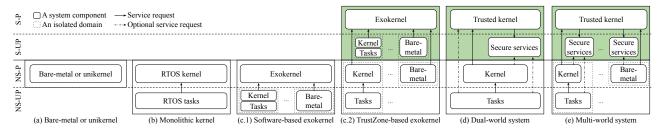

Figure 2: Identified Cortex-M software architectures in the collected dataset and in the literature. NS-UP: non-secure unprivileged, NS-P: non-secure privileged, S-UP: secure unprivileged, S-P: secure privileged.

## Vendor-Agnostic ISA Issues

**I03.** Fast state switch mechanism exploitable for privilege escalation: Cortex-M TrustZone uses the fast state switch technique to allow direct cross-state transitions from any privilege level without the need for a higher privileged secure monitor mode like Cortex-A TrustZone. Although this feature makes cross-state transitions more efficient, it exposes vulnerabilities to a recently discovered attack known as ret2ns [53]. This attack leverages critical system registers and instructions used by the fast state switch to escalate privilege in the non-secure state, potentially leading to arbitrary code execution.

**104.** Improper privilege management for inter-processor debugging: CVE-2018-18068 reports that the debugging host's privilege level is ignored in the inter-processor debugging mode, allowing the non-secure state on both TrustZone-M and TrustZone-A to gain access to the secure state resources via the ETM [54,55].

**105. Information leakage to the non-secure state due to state switches:** This could happen through memory and general-purpose and special registers: (i) if a region used by the secure state is re-mapped by MPC into the non-secure state without proper sanitization, sensitive information will be leaked; (ii) information leakage could happen if the general-purpose registers are not cleared when switching to the non-secure state. To address this issue, Arm recommends general-purpose registers that are not used to pass arguments should be cleared before state switches [7]; (iii) CVE-2021-35465 reports an issue of the floating-point lazy load multiple (VLLDM) instruction, which allows the non-secure code to access secure state floating-point registers.

#### Vendor-Specific Hardware Issues

**I06.** Improper privilege management in vendor-specific hardware features: Some hardware vendors introduce overpowerful hardware features that can be exploited to gain full control of the system. For example, NXP LPC55S6x MCUs include a ROM patch controller to fix bugs in the ROM after fabrication. CVE-2021-31532 reports that even attackers in the non-secure state and unprivileged level can utilize the ROM patch controller to reconfigure the SAU regions to gain privilege escalation. CVE-2022-22819 shows that the ROM patch controller firmware also has a buffer overflow bug that can lead to arbitrary code execution at the privileged level.

I07. Bypassable vendor-specific readback protection: Only M55 and M85 have the execute-only memory (XOM) feature, which prevents software or a hardware debugger from reading execute-only memory [56]. For MCUs before M55, some hardware vendors implement their own hardware units to prevent reading from the debug interface, a feature known as readback protection. For instance, the Nordic nRF51 series implements a mechanism to prevent debuggers from directly accessing flash and RAM address ranges. Notwithstanding, we found that only 32 out of the 1,458 Nordic samples in our dataset enable this feature. This protection, however, can be easily bypassed through arbitrary register read and write and single stepping in debugging [57]. Though the mechanism was improved in the nRF52 series [58], CVE-2020-27211 reports that a voltage glitch attack can still bypass it [51]. Similar mechanisms implemented by ST [59], NXP [60], and TI [61] are also bypassable by inferring instructions from the observed state transitions [62].

#### **Insights**

- Streamlined hardware mechanisms in Cortex-M, e.g., fast state switch, lead to new privilege management vulnerabilities and information leakage.

- The fragmentation of the Cortex-M ecosystem has brought in new security challenges: vendors aggressively introduce over-powerful hardware, which can undermine Cortex-M systems security if not properly designed.

#### 4 Software Architectural Issues

#### 4.1 Software Architectures

As shown in Figure 2, we identified two (i.e., a and b) software architectures in the collected firmware dataset and another three (i.e., c, d, and e) in the literature. *Bare-metal systems and unikernels* (a) run directly on the hardware at the highest (non-secure) privilege level. The RTOSs in such systems are only linked as a library OS, e.g., Mbed OS bare-metal profile [63]. We will discuss in 108 that over 99.44% of the 1,797 firmware belong to this category, including 66 firmware samples that use FreeRTOS and another 13 firmware use Mbed OS. *Monolithic kernels* (b) are the most common organization in microprocessor-based systems, e.g., Linux and Windows. Such systems run the kernel entirely at the

Table 2: Empirical Analysis of Security Features Adopted in Real-world Firmware

| Hardware Vendor                          |     | Nor<br>(Firm) | rdic<br>XRa | y)     | Other<br>Nordic |        |   | TI    |      |    | Telink  |    |        |     | Dia   | Dialog |       |   | NXP  | Cy  | press | ST   |   | Total |        |

|------------------------------------------|-----|---------------|-------------|--------|-----------------|--------|---|-------|------|----|---------|----|--------|-----|-------|--------|-------|---|------|-----|-------|------|---|-------|--------|

| Security Feature                         |     | #F            |             | #D     |                 | #F     |   | #F    | #D   |    | #F      |    | #D     |     | #F    |        | #D    |   | #F   |     | #F    | #F   |   |       | #F     |

| Readback Protection (I07)                | 17  | 2.21%         | 9           | 1.75%  | 15              | 2.17%  |   | -     | -    |    | -       |    | -      |     | -     |        | -     |   | -    |     | -     | -    |   | 32    | 1.78%  |

| Privilege Separation (I08)               | 8   | 1.04%         | 5           | 0.97%  | 2               | 0.29%  | 0 | 0%    | 0 0% | 0  | 0%      | 0  | 0%     | 0   | 0%    | 0      | 0%    | 0 | 0%   | 0   | 0%    | 0 0  | % | 10    | 0.56%  |

| SVC for Library Call (I09)               | 753 | 98.04%        | 500         | 97.47% | 690             | 100%   | 2 | 9.09% | 1 5% | 17 | 7 8.85% | 17 | 14.17% | 0   | 0%    | 0      | 0%    | 0 | 0%   | 2 2 | 2.99% | 2 50 | % | 1,466 | 81.58% |

| Stack Separation (I10)                   | 49  | 6.38%         | 34          | 6.63%  | 82              | 11.88% | 0 | 0%    | 0 0% | 0  | 0%      | 0  | 0%     | 3 : | 5.66% | 1      | 2.78% | 0 | 0%   | 0   | 0%    | 0 0  | % | 134   | 7.46%  |

| Stack Limit Register Usage (I10)         | 0   | 0%            | 0           | 0%     | 0               | 0%     | 0 | 0%    | 0 0% | 0  | 0%      | 0  | 0%     | 0   | 0%    | 0      | 0%    | 0 | 0%   | 0   | 0%    | 0 0  | % | 0     | 0%     |

| Task Stack Ovf. Guard* (I10)             | 59  | 96.72%        | 4           | 80%    | 9               | 32.14% |   | -     | -    |    | -       |    | -      |     | -     |        | -     |   | -    |     | -     | -    |   | 68    | 76.40% |

| Memory Access Control (MPU) (I12)        | 0   | 0%            | 0           | 0%     | 4               | 0.58%  | 0 | 0%    | 0 0% | 0  | 0%      | 0  | 0%     | 0   | 0%    | 0      | 0%    | 1 | 100% | 0   | 0%    | 0 0  | % | 5     | 0.28%  |

| Memory Access Control (sMPU) (I12)       | 19  | 2.47%         | 17          | 3.31%  | 0               | 0%     |   | -     | -    |    | -       |    | -      |     | -     |        | -     |   | -    |     | -     | -    |   | 19    | 1.10%  |

| Stack Canaries (I13)                     | 0   | 0%            | 0           | 0%     | 1               | 0.14%  | 0 | 0%    | 0 0% | 0  | 0%      | 0  | 0%     | 0   | 0%    | 0      | 0%    | 0 | 0%   | 0   | 0%    | 0 0  | % | 1     | 0.06%  |

| Proper Instruction Sync. Barriers† (I14) | 30  | 36.59%        | 16          | 27.12% | 68              | 40%    |   | -     | -    |    | -       |    | -      | 0   | 0%    | 0      | 0%    |   | -    |     | -     | -    |   | 98    | 34.88% |

#F: Number of firmware, #D: Number of devices, -: Not applicable, \*: The percentage is only based on firmware that use RTOS, †: The percentage is only based on firmware that update CONTROL with the MSR instruction.

privileged level, and applications run in (unprivileged) user space. However, only 0.56% of the firmware samples in our dataset fall into this category. Exokernels (c) run at the highest privilege level, virtualizing and allocating resources to RTOSs or bare-metal applications running at a lower privilege level. We will discuss two software-based exokernel projects, Hermes [64] and MultiZone [65], and two Cortex-M TrustZone-based exokernel projects, lLTZVisor [66, 67] and SBIs [68], in D05. Dual-world systems (d), which are enabled by TrustZone-M, run RTOSs and applications in the non-secure state, whereas secure OS/services run in the secure state. The Trusted Firmware for Cortex-M (TF-M) [69] is a reference implementation of this architecture. Multi-world systems (e) enable multiple equally-secure TEEs. We will discuss uTango [70], one prominent example of a multi-world TEE implementation leveraging TrustZone-M in D06.

#### **Insights**

Despite the research progress towards more secure architectures for Cortex-M systems, a large number of the real-world firmware in our dataset are simply bare-metal systems and unikernels.

#### 4.2 Architectural Issues

Software architectural issues refer to common limitations and flaws we found in real-world firmware.

#### Lack of Privilege Management

**I08.** No or weak privilege separation: As shown in Table 2, only 10 out of 1,797 samples in our dataset execute some code at the unprivileged level, and the others execute entirely at the privileged level. Due to the lack of spatial isolation and privilege separation, a bug anywhere may compromise the whole system, even reverting MPU settings.

**I09. SVC repurposing:** The SVC instruction is designed to escalate the execution level; however, executing this instruction at the privileged level also transfers the control to the SVC handler. Surprisingly, we find that 1,466 (81.58%) samples run everything at the privileged level and repurpose this feature to call library APIs, e.g., Nordic SoftDevice [71], instead of privilege escalation. The behavior is consistent across vendors, e.g., Nordic, TI, Telink, Cypress, and ST.

#### Lack of Memory Protections

I10. No or weak stack separation: RTOSs, such as FreeR-TOS [72] and Zephyr [73], support multi-tasking, so each task has its own stack. However, stack separation between the kernel and application is rarely used in bare-metal firmware. Armv8-M also introduces stack limit registers (PSPLIM and MSPLIM) to delimit the boundaries of stacks. However, no firmware in our dataset has been used them.

RTOS Implementations: We found that only a few RTOSs protect tasks' stacks, and only Zephyr optionally supports using stack limit registers. When stack guard is enabled, FreeR-TOS [74] and Mbed OS [75] insert a predefined delimiter to mark the boundary of each task's stack. Zephyr can use either PSPLIM or an MPU-configured memory guard to prevent overwriting beyond a task's stack [76].

Empirical Analysis on Real-world Firmware: 10 samples that adopt privilege separation (discussed in 108) leverage both the MSP- and PSP-based stacks. In addition, another 124 samples use both the MSP- and PSP-based stacks without privilege separation. All other samples (1,663; 92.54%) only adopt a single MSP-based stack. 59 of the 66 FreeRTOS-based firmware samples and 7 of the 13 Mbed OS-based firmware samples use task stack overflow guards.

I11. Secure state exception stack frame manipulation: CVE-2020-16273 shows that the non-secure state software may manipulate the secure stacks and hijack the secure control flow if the secure software does not properly initialize the secure stacks. To this end, an attacker creates a fake exception return stack frame to deprivilege an interrupt.

I12. No or weak memory access control; executable stack: Despite the presence of MPU, previous research suggests that it is rarely utilized in most real-world systems [77–79]. We confirm that 1,773 of the 1,797 firmware in our dataset do not use MPU, which means the code, SRAM, and RAM regions are executable and malicious code can read and write arbitrary memory. Out of the 24 firmware that use MPU in our dataset, five use the MPU defined by Arm. The remaining 19 use a vendor-specific implementation, i.e., Nordic's simplified

MPU (sMPU) [80], which only supports a subset of MPU features. Specifically, sMPU only supports read and write permissions with two protection domains.

I13. No or weak stack canary: Stack canary implementation involves initializing the canary value, runtime verification, and handling mismatches. The compiler and libraries manage the latter two, with the system initializing the canary value. In the standard C libraries (libc), the value of the stack canary is taken from a global variable \_\_stack\_chk\_guard. In modern OSs, the value of the canary is randomly initialized when a process is created. However, embedded systems often use a fixed canary value post-compilation or boot [81]. Notably, there is only one \_\_stack\_chk\_guard for the entire physical address space. We found that only *one* of the 1,797 firmware samples in our dataset adopts it.

I14. Missing barrier instructions: Barrier instructions, including data memory barrier (DMB), data synchronization barrier (DSB), and instruction synchronization barrier (ISB), guarantee that system configurations take effect before any memory operations [82]. The omission of them is unlikely to cause any issues on most Cortex-M MCUs because they do not have out-of-order execution and branch prediction capabilities. For MCUs that do have such capabilities, e.g., M7, this may lead to similar vulnerabilities that were discovered on microprocessors [83–85]. To check if barriers are set in firmware, for any CONTROL register update, we verify if there is an ISB instruction in its ten subsequent instructions. Our analysis shows that only 98 of the 281 firmware samples (34.88%) that update the CONTROL register use the ISB instruction thereafter. However, as we cannot confirm which architecture those firmware are using, it is unclear whether the missing barrier instructions will cause issues or not.

#### **Insights**

- The real-world firmware samples in our dataset barely use the security features of Cortex-M and largely lack the security mitigations that are widely deployed on modern microprocessor-based systems.

- Some software- and compiler-based mitigations, e.g., stack canaries, are less effective on MCU-based systems and should be redesigned.

## **5 Software Implementation Issues**

Table 3 presents the numbers of Cortex-M related CVEs affecting nine hardware vendors, seven RTOSs, and two TLS libraries. We break down the number based on CVSS scores [86]. As shown in Table 3, the majority of CVEs (53.85%) affecting hardware vendors are classified as "medium" severity, while the majority of CVEs affecting RTOSs (78.07%) are categorized as either "critical" or "high". We use a bug classification system proposed in [4] to characterize them into three major classes, i.e., validation, functional, and extrinsic. We summarize the results in Table 4, where we

Table 3: Distribution of disclosed Cortex-M related CVEs (2017 - 2023)

| HW Vendor/RTOS/Lib    | (    | Critical |     | High   | M   | ledium   |   | Low    |     | Total  |  |

|-----------------------|------|----------|-----|--------|-----|----------|---|--------|-----|--------|--|

| Arm                   | 0    | 0%       | 4   | 57.14% | 2   | 28.57%   | 1 | 14.29% | 7   | 1.99%  |  |

| Microchip Technology  | 1    | 14.29%   | 2   | 28.57% | 4   | 57.14%   | 0 | 0%     | 7   | 1.99%  |  |

| Silicon Labs          | 6    | 40.00%   | 2   | 13.33% | 6   | 40.00%   | 1 | 6.67%  | 15  | 4.27%  |  |

| NXP Semiconductors    | 1    | 7.69%    | 6   | 46.15% | 6   | 46.15%   | 0 | 0%     | 13  | 3.70%  |  |

| ST Microelectronics   | 2    | 12.50%   | 2   | 12.50% | 12  | 75.00%   | 0 | 0%     | 16  | 4.56%  |  |

| Cypress Semiconductor | 0 09 | 0%       | 6   | 50.00% | 6   | 50.00% 0 |   | 0%     | 12  | 3.42%  |  |

| Gigadevice            | 0    | 0%       | 0   | 0%     | 6   | 100.00%  | 0 | 0%     | 6   | 1.71%  |  |

| Texas Instruments     | 0    | 0%       | 6   | 54.55% | 5   | 45.45%   | 0 | 0%     | 11  | 3.13%  |  |

| Nordic                | 0    | 0%       | 2   | 50.00% | 2   | 50.00%   | 0 | 0%     | 4   | 1.14%  |  |

| Subtotal (HW vendors) | 10   | 10.99%   | 30  | 32.97% | 49  | 53.85%   | 2 | 2.20%  | 91  | 25.93% |  |

| FreeRTOS              | 3    | 15.79%   | 9   | 47.39% | 7   | 36.84%   | 0 | 0%     | 19  | 5.41%  |  |

| CMSIS RTOS2           | 1    | 100.00%  | 0   | 0%     | 0   | 0%       | 0 | 0%     | 1   | 0.28%  |  |

| Mbed OS               | 6    | 60.00%   | 4   | 40.00% | 0   | 0%       | 0 | 0%     | 10  | 2.85%  |  |

| Zephyr                | 17   | 23.61%   | 36  | 50.00% | 18  | 25.00%   | 1 | 1.39%  | 72  | 20.51% |  |

| RIOT-OS               | 10   | 33.33%   | 18  | 60.00% | 2   | 6.67%    | 0 | 0%     | 30  | 8.55%  |  |

| Contiki-ng            | 16   | 39.02%   | 18  | 43.90% | 7   | 17.07%   | 0 | 0%     | 41  | 11.68% |  |

| Azure                 | 5    | 35.71%   | 3   | 21.43% | 5   | 35.71%   | 1 | 7.14%  | 14  | 3.99%  |  |

| Subtotal (RTOSs)      | 58   | 31.01%   | 88  | 47.06% | 39  | 20.86%   | 2 | 1.07%  | 187 | 53.28% |  |

| Mbed TLS              | 6    | 20.69%   | 12  | 41.38% | 11  | 37.93%   | 0 | 0%     | 29  | 8.26%  |  |

| WolfSSL               | 10   | 22.73%   | 14  | 31.82% | 20  | 45.45%   | 0 | 0%     | 44  | 12.54% |  |

| Subtotal (Libs)       | 16   | 21.92%   | 26  | 35.62% | 31  | 42.47%   | 0 | 0%     | 73  | 20.80% |  |

| Total                 | 84   | 23.93%   | 144 | 41.03% | 119 | 33.90%   | 4 | 1.14%  |     | 351    |  |

further provide a breakdown of bugs based on the functionality and the software components.

## **5.1** Validation bugs

Validation bugs refer to bugs that mishandle or improperly validate input and output data. Examples are out-of-bounds read and write and improper parameter validation. They are frequently exploited for arbitrary write and read, allowing attackers to steal/overwrite sensitive information, execute remote code, or cause a denial of service.

**115.** Validation bugs in communication components: Table 4 shows that 57.78% of validation bugs affect communication stacks, e.g., Bluetooth and TCP/IP implementations. For instance, FreeRTOS has a DNS poisoning bug that does not check if a DNS answer matches an outgoing query (CVE-2018-16598). Open-source libraries that are heavily used by Cortex-M systems, such as Mbed TLS or WolfSSL, also have 42 validation bugs.

**116. Validation bugs in device drivers:** Device drivers are exposed to attackers through physically-accessible peripherals, e.g., the USB interface. We found 25 bugs that affect two hardware vendors and two RTOSs in this category. For instance, the buffer overread bug of the NXP Kinetis K82 USB driver can be leveraged to access the flash (CVE-2021-44479). The USB driver in Zephyr also has a buffer overflow bug that allows a USB-connected host to cause possible remote code execution (CVE-2020-10019).

**I17.** Validation bugs in dynamic memory allocations: Embedded systems commonly implement custom allocators rather than using the standard heap implementations in the Libc [16]. Bugs in heap management can result in a system crash or arbitrary code execution. For example, NXP's SDK, RIOT-OS, Mbed OS, and CMSIS RTOS are vulnerable to integer overflows in their allocator functions [87].

| Bug Class Functions |                         | Affected HW Vendors' SDKs                                                             | #.                                                                                                     | Bugs |        |

|---------------------|-------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|--------|

|                     | Communication           | NXP (2), Microchip (5), ST (1), TI (9),<br>Cypress (10), Silicon Libs (8), Nordic (3) | FreeRTOS (11), RIOT-OS (24), Mbed OS (7), Zephyr (32),<br>Contiki-ng (39), Mbed TLS (14), wolfSSL (28) | 193  | 57.78% |

|                     | Device Driver           | TF-M (1), NXP (4), ST (7)                                                             | Zephyr (8), Azure (5)                                                                                  | 25   | 7.48%  |

| Validation          | Memory Allocation       | NXP (1)                                                                               | FreeRTOS (2), RIOT-OS (2), Mbed OS (2),<br>CMSIS RTOS2 (1), Zephyr (2)                                 | 10   | 2.99%  |

|                     | Context Switch          | TF-M (2)                                                                              | FreeRTOS(1), Zephyr (3)                                                                                | 6    | 1.79%  |

|                     | Others                  | Silicon Labs(5), NXP (2), Microchip (1)                                               | Contiki-ng (1), Zephy (10), Azure (9)                                                                  | 28   | 6.59%  |

| Eventional          | Protocol Implementation | TI (1), Cypress (2), Silicon Labs (2)                                                 | FreeRTOS (3), RIOT-OS (4), Zephyr (13), Mbed OS (1),<br>Mbed TLS (3), wolfSSL (9)                      | 38   | 11.38% |

Table 4: Distribution of Cortex-M software CVEs in different classes

**I18. Validation bugs in context switch components:** Bugs in these components have been exploited for privilege escalation. Zephyr uses signed integer comparison to validate the syscall number, so a negative number leads to privilege escalation (CVE-2020-10027). TF-M has a bug allowing for out-of-bounds write in an NSC function, which can lead to data leakage from the secure state (CVE-2021-27562).

Memory Access Control

Cryptography Primitive

Software Side-Channel

TF-M (1), NXP (1), ST (1)

TF-M (2), Microchip (1), ST (1)

I19. Validation bugs in other components: As discussed in 108, many systems execute entirely at the privileged level, and bugs in any component could lead to severe consequences. For example, a buffer overflow in FreeRTOS' shell can cause privileged code execution (CVE-2020-10023). Microchip's SDK has integer overflows that can be leveraged to access flash memory (CVE-2019-16127).

#### 5.2 **Functional bugs**

Functional

Extrinsic

Functional bugs refer to programming errors that do not correctly implement the intended design.

**I20.** Functional bugs in protocol implementations: 11.38% of the functional bugs are related to protocol implementations. For instance, the Bluetooth controller in the Cypress SDK uses a much shorter random number (than 128 bits) as the paring number, allowing the brute force of the random number to perform a man-in-the-middle attack during BLE pairing (CVE-2020-11957).

**I21. Functional bugs in memory access control:** Incorrect memory access control configurations, including for MPU and TrustZone, compromise isolation. We found eight bugs affecting one hardware vendor and two RTOSs in this category. For example, FreeRTOS has a bug that allows any code to set the system privilege level (CVE-2021-43997).

I22. Functional bugs in cryptography primitives: We found four bug reports in this category. For instance, RIOT-OS has a nonce reuse bug in its encryption function (CVE-2021-41061) and TF-M has a functional bug when cleaning up the memory allocated for a multi-part cryptographic operation, resulting in a memory leak (CVE-2021-32032). The implementations of PKCS #1 v1.5 padding for RSA in the ST (CVE-2020-20949) and Microchip (CVE-2020-20950) SDKs are vulnerable to the Bleichenbacher attack [88]. This vulnerability relies on the use of error messages or responses

from the server to gain information about the validity of the padding after decryption attempts.

10

12

2 99%

3.59%

4.19%

## 5.3 Extrinsic bugs

Mbed TLS (4), wolfSSL (4)

Mbed TLS (8), wolfSSL (5)

FreeRTOS (2), Zephyr (4), Contiki-ng (1)

Extrinsic bugs refer to defects that do not belong to the validation bugs or functional errors.

**I23. Software side-channels:** The Lucky 13 attack in Mbed TLS (CVE-2020-16150 and CVE-2020-36423) enables an attacker to deduce secret key information by exploiting time variations in the decryption process. This vulnerability, specifically found in Cipher Block Chaining (CBC) mode, is based on the time differences associated with padding length.

#### **Insights**

- Most Cortex-M based production systems are written in memory-unsafe languages, e.g., C [89], and they suffer from memory corruption vulnerabilities.

- Microcontrollers lack security mechanisms present in microprocessors for decades, such as privilege separation Microcontroller developers may not realize the absence of features like an MMU can pose greater risks than microprocessors. Without privilege separation, any bug can be critical and compromise the entire system.

## **Security Research**

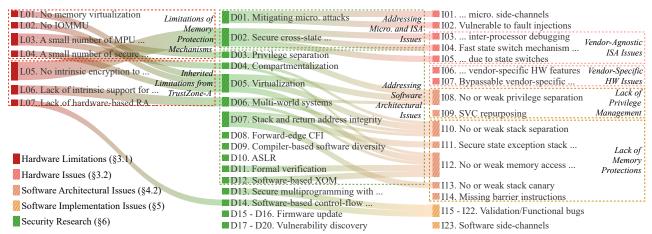

We present a taxonomy of the security research projects on Cortex-M systems. Figure 3 depicts and summarizes the relationships among limitations, issues, and mitigations at different layers. Table 5 presents a comparative evaluation.

Addressing Hardware Issues

#### 6.1 Addressing Microarchitectural and ISA Issues

**D01. Mitigating microarchitectural attacks:** To mitigate information leakage through timing side-channels (I01), BUSted [47] recommends disabling DMA during sensitive execution, and introducing random delays. To counter information leakage through long-term data remanence, UnTrust-Zone [48] suggests initializing SRAM at startup. To mitigate

Figure 3: The relationships among the systematized Cortex-M related limitations, issues, and mitigations. The connections indicate the issues a research direction attempts to address and the limitations it needs to overcome. For instance, to address the issue of *no or weak privilege separation* (108), mitigations (D03, D05, and D06) have been proposed, and they overcome some limitations (L01, L02, and L03). An interactive version of this figure can be accessed at our anonymized repo.

fault injection attacks (I02), one strategy is the use of duplicate security-critical registers [131].  $\mu$ Glitch suggests introducing random delays in the execution code to complicate the parameter determination process for fault injections.

**D02.** Secure cross-state control and data interactions: One effective way to counteract privilege escalation through fast state switching (I03) is to add additional privilege checks. Ret2ns [53] suggests using address masking and MPU configuration checks to limit return targets from secure to nonsecure state at the non-secure unprivileged level. In improving privilege management for inter-processor debugging (I04), Nailgun [55] employs MPU to restrict low-privilege access to debug registers. To mitigate information leakage during cross-state switches (I05), one approach is to implement authentication and authorization between the two states, as Se-CReT [132] does for TrustZone-A. Secure Informer [95] and ShieLD [96] authenticate secure service calls from the nonsecure state by verifying non-secure MPU configurations.

Addressing Software Architectural Issues

#### **6.2** Separation of Privilege

Projects in this category provide different levels of granularity in isolating and confining software modules of *one* bare-metal system or *one* RTOS to address 108.

**D03. Privilege separation:** Solutions were proposed to automatically relegate RTOS tasks and bare-metal systems to the unprivileged level and use MPU to govern memory access. SAFER SLOTH [97] dispatches tasks as interrupt handlers and lowers the privilege level in the interrupt service routine. EPOXY [77] automatically identifies operations requiring privileged execution (e.g., MSR, move to system registers from general-purpose registers) in bare-metal systems. It then relegates the whole bare-metal system to the unprivileged level and instruments privilege escalation and relegation instructions around the operations requiring privileged execution.

These privilege separation approaches only introduce a small number of context switches, introducing low overhead.

**D04.** Compartmentalization: The projects on privilege separation (D03) only split a program into privileged and unprivileged parts. However, software modules at the same privilege level still reside in the same security and fault domain, resulting in coarse-grained memory access control (I12). Several compartmentalization solutions attempt to address this issue.

Compartmentalization with heavy context switches: uSFI compiler [98] instruments an entry function for each module and changes cross-module procedure calls to SVC instructions. ACES [79] instruments binaries to enforce inter-component isolation. MINION [99] automatically identifies the reachable memory regions of tasks through static analysis and enforces run-time memory access control. Because there are limited available MPU regions (L03), ACES and MINION propose schemes to merge the compartments. Compared to D03, compartmentalization introduces more context switches between modules; hence, the overhead is higher.

Compartmentalization with reduced context switches: To reduce the overhead introduced by compartmentalization, OPEC [100] leverages global variable shadowing to minimize the need for MPU regions and compartmentalizes programs to include only essential functions. EC [101] uses a formally verified microkernel and intra-kernel isolation to achieve compartmentalization. CRT-C [102] compartments an RTOS into kernel, threads, and device drivers and utilizes CheckedC [133] to restrict their programming capabilities.

DMA-enabled compartmentalization: The aforementioned compartmentalization solutions do not support DMA, leaving the system vulnerable to malicious DMA-capable devices due to the absence of an IOMMU (L02). D-Box [103] addresses this issue by introducing more secure MPU configurations and kernel extensions with explicit support for DMA operations.

Table 5: Comparative evaluation of system isolation and attack mitigation projects for Cortex-M (§6.2 - §6.8). The first column of the table lists the major defense mechanism proposed or adopted in a project.

|             |                                  |              |                |                                   |                                 |                                | §3                                | .1                                | <b>§</b> 3                    | .2                              | §.                           | 4.2                     | §               | 5              |     | oo.                                            |            |                                | Self-rep        | orted a                     | verage                  | or wor | st case    | overh         | ead (%            | 6)                          |

|-------------|----------------------------------|--------------|----------------|-----------------------------------|---------------------------------|--------------------------------|-----------------------------------|-----------------------------------|-------------------------------|---------------------------------|------------------------------|-------------------------|-----------------|----------------|-----|------------------------------------------------|------------|--------------------------------|-----------------|-----------------------------|-------------------------|--------|------------|---------------|-------------------|-----------------------------|

|             | Project                          | Year         | Venue          | Input (S: source code; B: binary) | Target (B: bare-metal; R: RTOS) | Prototype Implementation (ISA) | Limit. of Memory Prot. Mechanisms | Inherited Limit. from TrustZone-A | Vendor-Agnostic Micro. Issues | Vendor-specific Hardware Issues | Lack of Privilege Management | Lack Memory Protections | Validation Bugs | Extrinsic Bugs | MPU | Unprivileged Store/Load Instructions TrustZone | DWT<br>FPB | Code, Binary Size Increasement | Memory Overhead | Energy Consumption Overhead | Bare-metal Applications | RTOSs  | BEEBS [90] | CoreMark [91] | CoreMark-Pro [92] | Dhrystone [93] Embench [94] |

| D01         | BUSted [47]<br>UnTrustZone [48]  | 2023<br>2023 | S&P            | -                                 | -                               | v8<br>-                        |                                   |                                   | ✓<br>✓                        |                                 |                              |                         |                 |                |     | +                                              |            |                                |                 |                             |                         |        |            |               |                   |                             |

|             | μGlitch [52]<br>Nailgun [55]     | 2023         | USENIX<br>TDSC | S                                 | R                               | v7                             |                                   |                                   | <u> </u>                      | /                               |                              | . /                     |                 |                | +   |                                                |            |                                |                 |                             |                         |        |            |               |                   |                             |

|             | ret2ns [53]                      |              | DAC            | S                                 | R                               | v8                             |                                   |                                   | ~                             |                                 |                              | ✓<br>✓                  |                 |                | +   | +                                              |            |                                |                 |                             |                         |        |            |               |                   |                             |

| D02         |                                  | 2022         | CPSS           | S                                 | R                               | v8                             |                                   | ~                                 | ~                             | /                               |                              | ~                       |                 |                | +   | +                                              |            | <.01                           |                 |                             |                         | 3.5    |            |               |                   |                             |

|             | ShieLD [96]                      | 2022         | TDSC           | S                                 | R                               | v8                             |                                   | ~                                 | V                             | /                               |                              | ~                       |                 |                | +   | +                                              |            | .04                            |                 |                             |                         | 2600   |            |               |                   |                             |

| D03         | SAFER SLOTH [97]                 | 2014         | RTAS           | S                                 | R                               | v7                             |                                   |                                   |                               |                                 | <b>-</b>                     | ~                       |                 |                | +   |                                                |            |                                |                 |                             |                         | >100   |            |               |                   |                             |

| D03         | EPOXY [77]                       | 2017         | S&P            | S                                 | В                               | v7                             |                                   |                                   |                               |                                 | /                            | ~                       |                 |                | +   |                                                |            | 29                             | 29              | 2.6                         | 2.4                     |        | 1.6        |               |                   |                             |

|             | uSFI [98]                        | 2018         | DATE           | S                                 | R                               | v7                             |                                   |                                   |                               |                                 | ~                            | ~                       |                 |                | +   | +                                              |            | 10                             |                 |                             |                         | 1.1    |            |               |                   |                             |

|             | ACES [79]                        | 2018         | USENIX         | S                                 | В                               | v7                             | ~                                 |                                   |                               |                                 | ~                            | ~                       |                 |                | +   |                                                |            | 70                             |                 |                             | 13                      |        |            |               |                   |                             |

| <b>.</b>    | MINION [99]                      |              | NDSS           | S                                 | R                               | v7                             | <b>/</b>                          |                                   |                               |                                 | /                            | ~                       |                 |                | +   |                                                |            | -71.3                          | -98.86          |                             | 22                      | 6.13   |            |               |                   |                             |

| D04         | OPEC [100]<br>EC [101]           | 2022<br>2023 | EuroSys<br>S&P | S                                 | B<br>B/R                        | v7<br>v7                       | ~                                 |                                   |                               |                                 | <b>/</b>                     | ✓                       |                 |                | +   |                                                | +          | 1.79                           | 5.53<br>2.57    |                             | .23                     |        |            |               |                   |                             |

|             | CRT-C [102]                      | 2023         |                | S                                 | R                               | v7                             | •                                 |                                   |                               |                                 | /                            |                         |                 |                | '   |                                                |            |                                | 1.75            |                             |                         | 2.63   |            |               |                   |                             |

|             | D-Box [103]                      |              | NDSS           | S                                 | R                               | v7                             | ~                                 |                                   |                               |                                 | /                            | ~                       |                 |                | +   |                                                |            | 12                             | 07              | -18.2                       |                         | 2      |            |               |                   |                             |

| 1           | Hermes [64]                      | 2018         | MCSA           | S                                 | B/R                             | v7                             | ~                                 |                                   |                               |                                 | ~                            | ~                       |                 |                | +   |                                                |            |                                |                 |                             |                         |        |            |               |                   |                             |

| D05         | MultiZone [65]                   | 2020         | EW             | В                                 | В                               | v7                             | ~                                 |                                   |                               |                                 | /                            | ~                       |                 |                | +   |                                                |            |                                |                 |                             | .01                     |        |            |               |                   |                             |

|             | lLTZVisor [66, 67]               |              | RTAS           |                                   | B/R                             | v8                             | ~                                 |                                   |                               |                                 | ~                            |                         |                 |                |     | +                                              |            |                                |                 |                             |                         | .6     |            |               |                   |                             |

|             | SBIs [68]                        | 2022         | RTAS           |                                   | B/R                             | v8                             | ~                                 |                                   |                               |                                 | <b>/</b>                     | ~                       |                 |                | +   | +                                              |            |                                |                 |                             |                         |        |            |               |                   |                             |

| D06         | RT-TEE [104]<br>SafeTEE [105]    | 2022<br>2022 | S&P<br>DATE    | S                                 | R<br>R                          | v8<br>v8                       | ✓<br>✓                            |                                   |                               |                                 | Y                            | ✓<br>✓                  |                 |                |     | +                                              |            |                                |                 |                             |                         |        |            |               |                   | 2.5                         |

| Doo         | uTango [70]                      | 2022         | Access         |                                   | B/R                             | v8                             |                                   | <u> </u>                          |                               |                                 | Ľ                            | ~                       |                 |                | +   | +                                              |            | 4.6                            |                 |                             |                         |        |            |               |                   | .05                         |

|             | CaRE [106]                       |              | RAID           | В                                 | В                               | v8                             | Ť                                 | Ť                                 |                               |                                 | Ť                            | ~                       | /               |                | +   | +                                              |            | 14.5                           |                 |                             | 369                     |        |            |               |                   | 513                         |

|             | Silhouette [107]                 |              | USENIX         | S                                 | В                               | v7                             |                                   |                                   |                               |                                 |                              | ~                       | /               |                |     | +                                              |            | 8.9                            |                 |                             |                         | •      | 3.4        |               | 1.3               |                             |

| <b>D</b> 07 | TZmCFI [108]                     | 2020         |                | S                                 | R                               | v8                             |                                   |                                   |                               |                                 |                              | $\checkmark$            | ~               |                | +   | +                                              |            |                                |                 |                             |                         | 84     |            | 14.14         |                   |                             |

| DUI         | Kage [109]                       |              | USENIX         | S                                 | R                               | v7                             |                                   |                                   |                               |                                 |                              | ~                       | ~               |                |     | +                                              |            | 49.8                           |                 |                             |                         | 5.2    |            |               |                   |                             |

| D08         | SUM [110]                        | 2023         | C&S            | S                                 | В                               | v7                             |                                   |                                   |                               |                                 |                              | ~                       | <b>/</b>        |                | +   |                                                |            | 8.33                           |                 |                             | 2.77                    | 2.63   |            |               |                   |                             |

|             | SHERLOC [111]<br>μRAI [112]      | 2023         | CCS<br>NDSS    | S                                 | B/R<br>B                        | v8<br>v7                       |                                   |                                   |                               |                                 |                              | ✓<br>✓                  | ✓<br>✓          |                | +   | +                                              | +          | 54.1                           | 15.2            |                             | .1                      | 1106   |            | 8.1           |                   |                             |

|             | RIO [113]                        | 2023         | Access         | S                                 | В                               | v8                             |                                   |                                   |                               |                                 |                              | <i>-</i>                |                 |                | '   | +                                              |            | 29.9                           | 13.2            |                             | 16.83                   |        |            | 0.1           |                   |                             |

| D09         | Randezvous [114]                 | 2022         | EuroS&P        | S                                 | В                               | v7/8                           |                                   |                                   |                               | _                               |                              | <b>/</b>                | /               |                | +   |                                                | +          | 13.6                           | 24.5            |                             | 0.6                     |        | 6.9        |               | 7.0               |                             |

| ↓<br>D10    | HARM [115]                       | 2022         | EuroS&P        | В                                 | B/R                             | v8                             |                                   |                                   |                               |                                 |                              | ~                       | ~               |                | +   | +                                              |            | 15.49                          |                 |                             | 5.8                     | 21     | 28         |               |                   |                             |

|             | fASLR [116, 117]                 | 2022         | ESORICS        | S                                 | В                               | v8                             |                                   |                                   |                               |                                 |                              | $\checkmark$            | ~               |                | +   | +                                              | -          |                                | 4.73            |                             | 9.65                    |        |            |               |                   |                             |

| D11         | Pip-MPU [118]                    |              | IJESA          |                                   |                                 | v7/8                           |                                   |                                   |                               |                                 |                              | ~                       |                 |                | +   |                                                |            |                                |                 |                             |                         |        |            |               |                   |                             |

| D12         | uXOM [119]                       |              | USENIX         | S                                 | R                               | v7                             | <b>/</b>                          |                                   |                               |                                 |                              | ~                       | <b>/</b>        |                |     | +                                              |            | 15.7                           |                 | 7.5                         | 02                      |        | 7.3        |               | 1.1               |                             |

|             | PicoXOM [120]                    |              | SecDev         | _                                 | B/R                             | v7                             | _                                 | _                                 |                               |                                 | <u> </u>                     | <u> </u>                | _               |                | +   |                                                | +          | 5.89                           |                 |                             | .02                     |        | 0.46       |               | 11                |                             |

| D13         | Tock [121]                       |              | SOSP           | S                                 | R                               | v7                             | ~                                 |                                   |                               |                                 | ~                            | ~                       | <b>/</b>        |                | +   |                                                |            |                                |                 |                             |                         | 400    |            |               |                   |                             |

|             | DIAT [122]<br>LAPE [123]         | 2019         | NDSS<br>HPCC   | S                                 | R<br>B                          | v7<br>v7                       | <b>/</b>                          |                                   |                               |                                 |                              | <b>/</b>                | ✓<br>✓          |                | +   |                                                |            | 38                             | 8.2             |                             | 2.2                     | 400    |            |               |                   |                             |

| D14         | ISC-FLAT [124]                   |              | RTAS           | S                                 | В                               | v8                             | /                                 |                                   |                               |                                 | ~                            | ✓<br>✓                  |                 |                | +   | +                                              |            | 30                             | 0.2             | 17.5                        |                         |        |            |               |                   |                             |

|             | ARI [125]                        |              | USENIX         | S                                 | R                               | v7                             | ~                                 |                                   |                               |                                 |                              | ~                       | /               |                | +   | +                                              |            |                                | 12.5            | 17.13                       | 10.7                    |        |            |               |                   |                             |